Question: VHDL Write the VHDL code for 4 bit binary counter. Inputs are X and the system clock. When X = 0, the counter is reset

VHDL

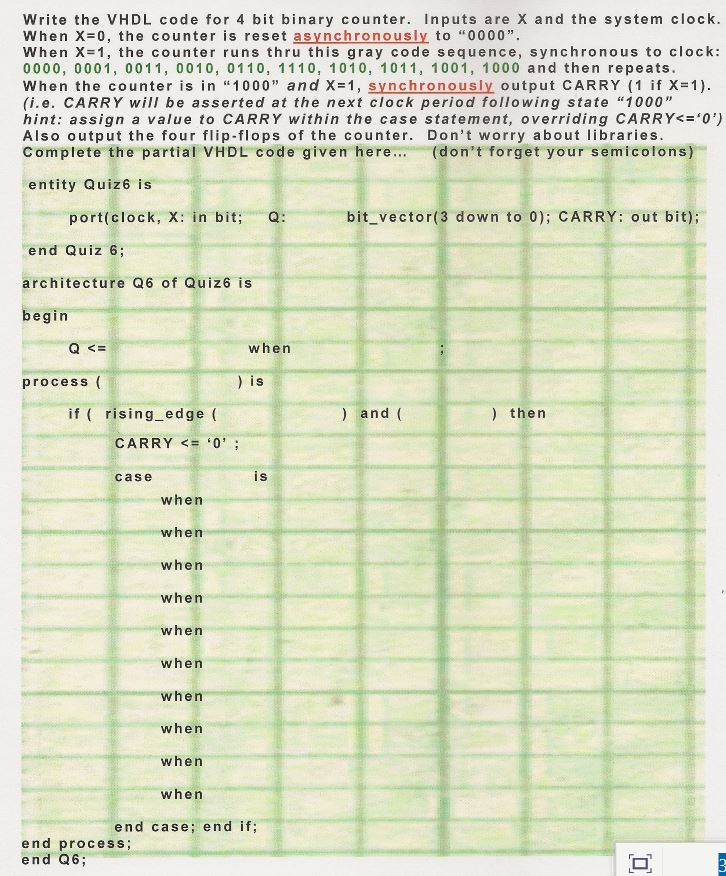

Write the VHDL code for 4 bit binary counter. Inputs are X and the system clock. When X = 0, the counter is reset asynchronously to "0000". When X = 1, the counter runs thru this gray code sequence, synchronous to clock: 0000,0001,0011,0010, 0110, 1110, 1010, 1011, 1001, 1000 and then repeats. When the counter is in "1000" and X = 1, synchronous output CARRY (1 if X = 1). (i, e. CARRY will be asserted at the next clock period following state "1000" Complete the partial VHDL code given here... (don't forget your semicolons) entity Quiz6 is port(clock, X: in bit; Q: bit_vector (3 down to 0); CARRY: out bit); end Quiz 6; architecture Q6 of Quiz6 is begin Q

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts