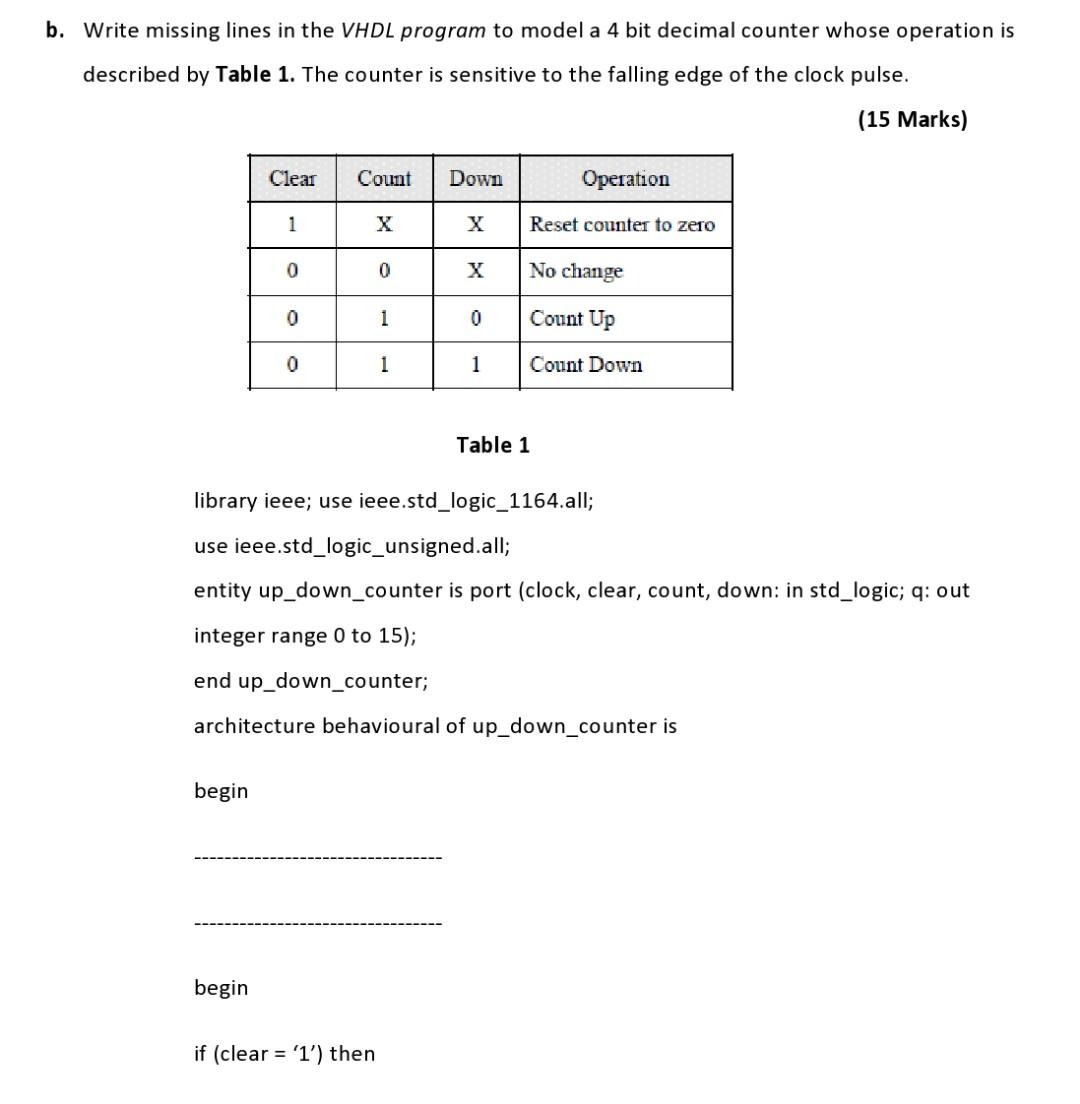

Question: VHDL programming b. Write missing lines in the VHDL program to model a 4 bit decimal counter whose operation is described by Table 1. The

VHDL programming

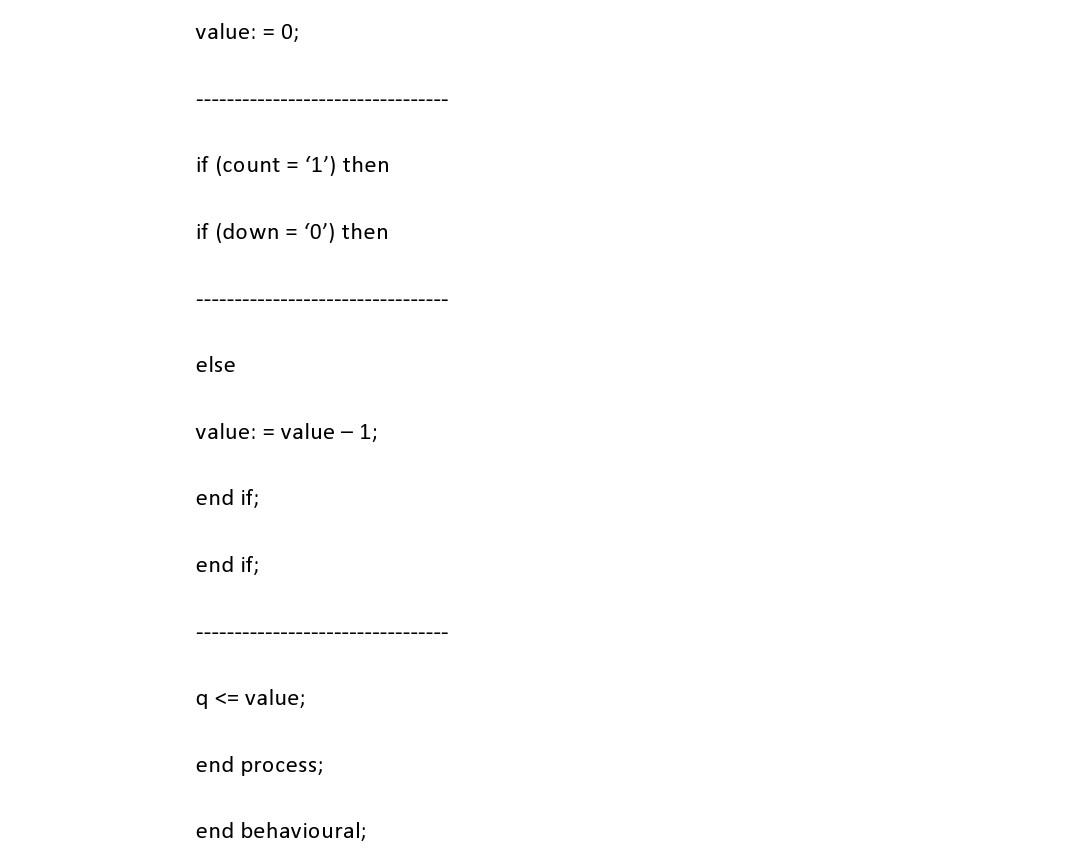

b. Write missing lines in the VHDL program to model a 4 bit decimal counter whose operation is described by Table 1. The counter is sensitive to the falling edge of the clock pulse. (15 Marks) Clear Count Down Operation 1 X Reset counter to zero 0 0 No change 0 1 0 Count Up 0 1 1 Count Down Table 1 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity up_down_counter is port (clock, clear, count, down: in std_logic; q: out integer range 0 to 15); end up_down_counter; architecture behavioural of up_down_counter is begin begin if (clear = '1') then value: = 0; if (count = '1') then if (down = '0') then else value: = value - 1; end if; end if; q

Step by Step Solution

There are 3 Steps involved in it

To complete the VHDL program for the 4bit decimal counter described you need to ... View full answer

Get step-by-step solutions from verified subject matter experts