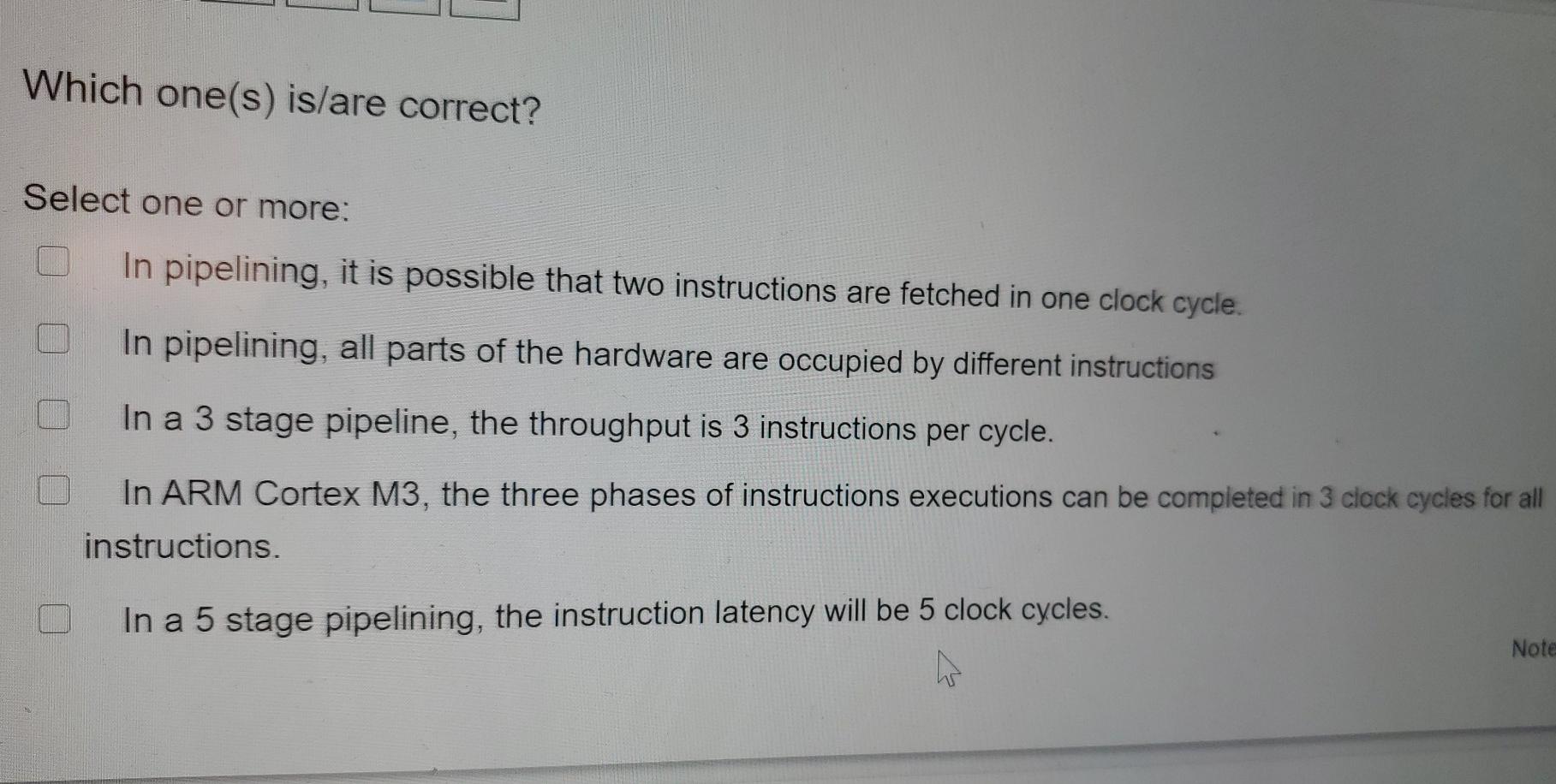

Question: Which one(s) is/are correct? Select one or more: In pipelining, it is possible that two instructions are fetched in one clock cycle. In pipelining, all

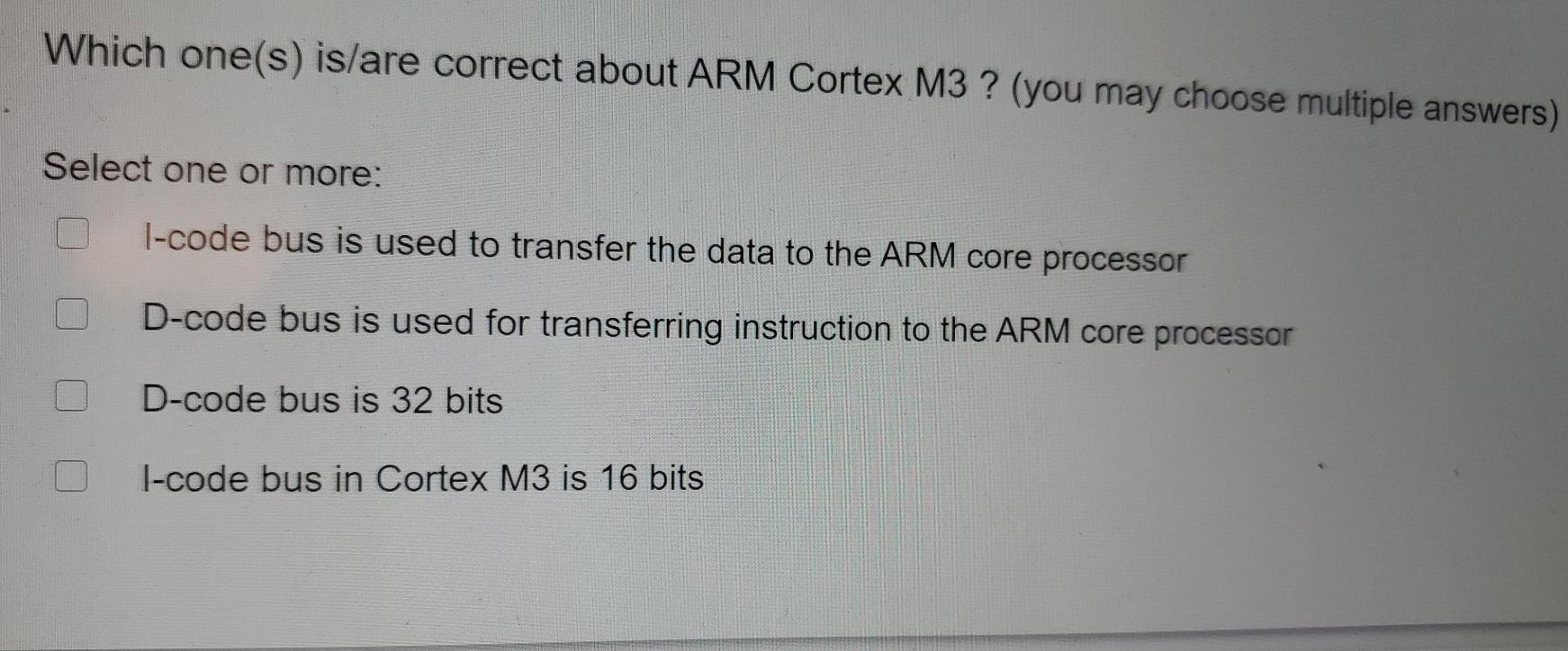

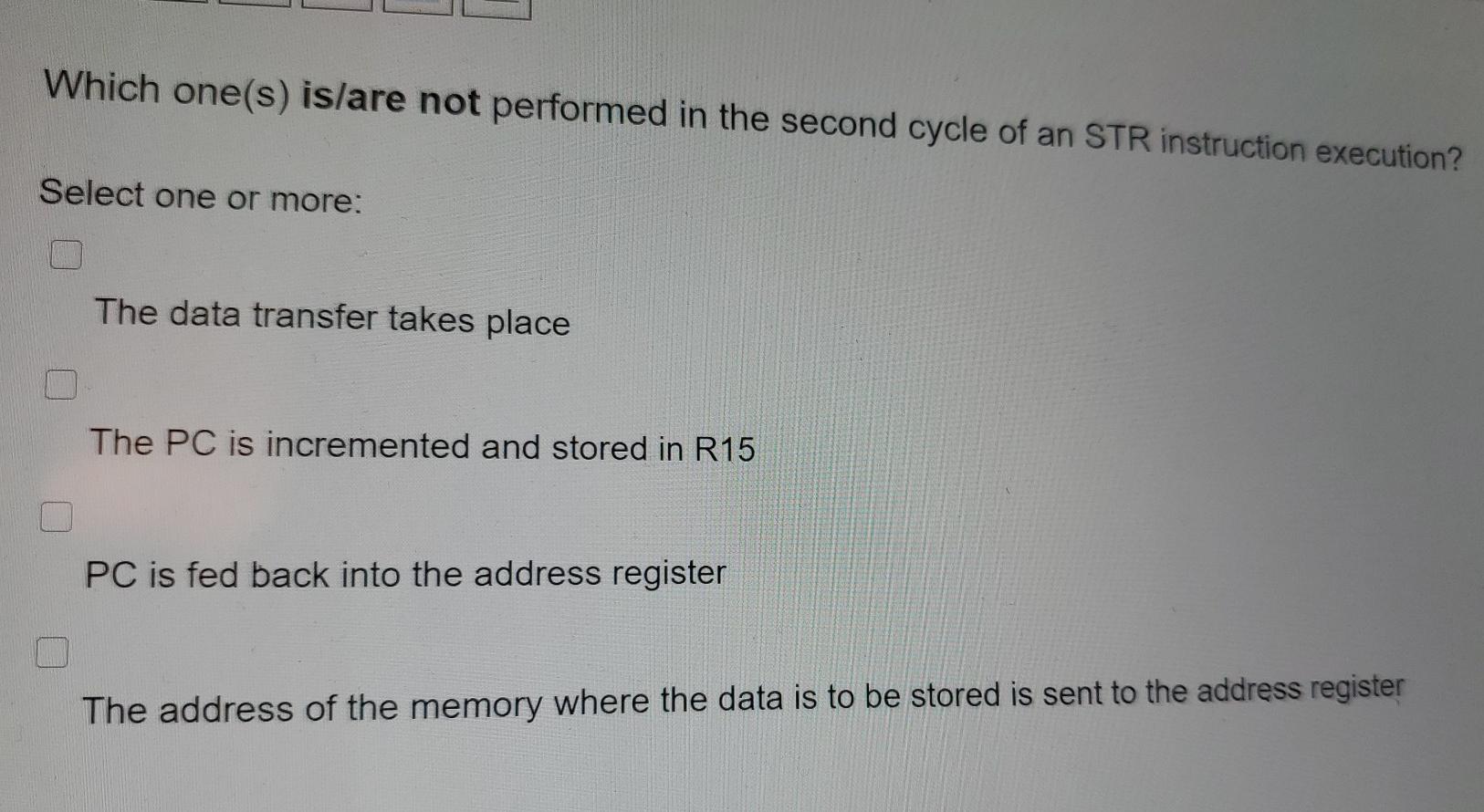

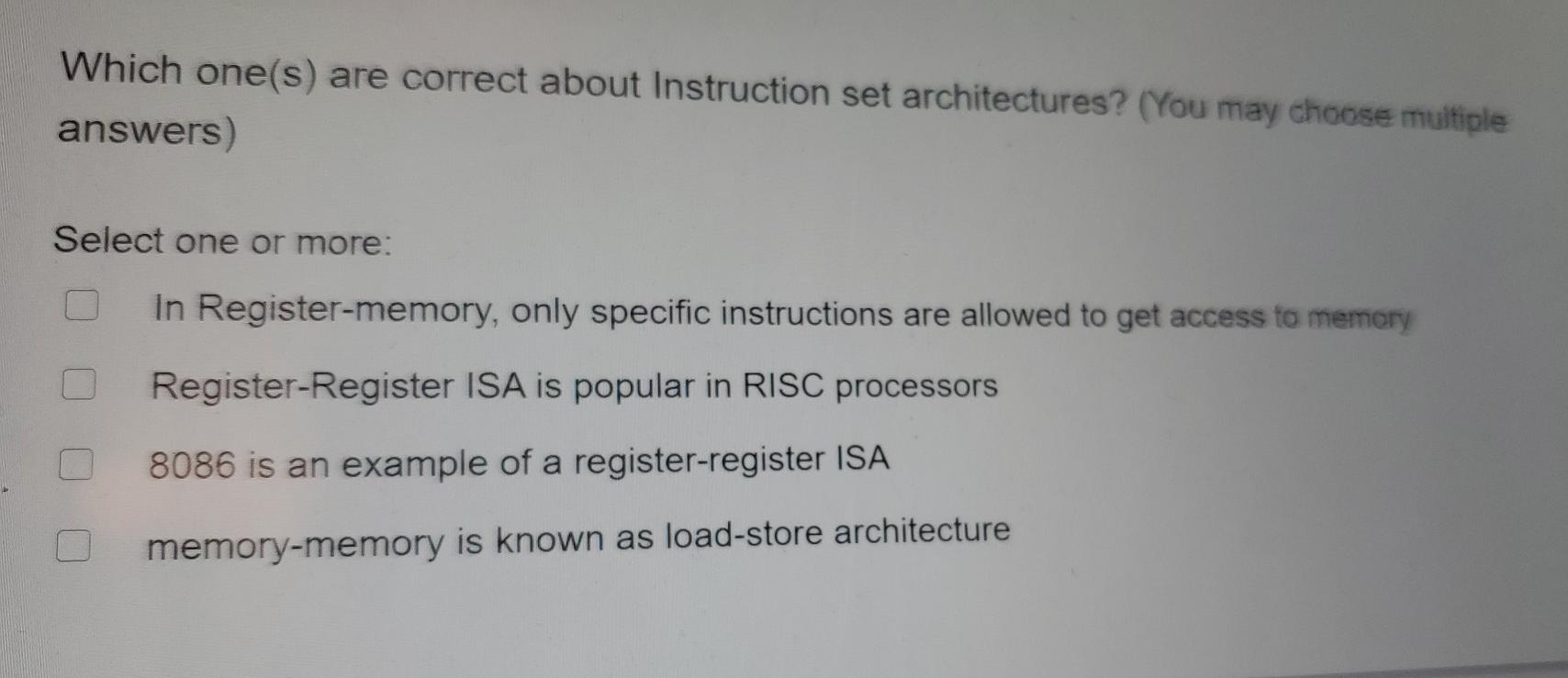

Which one(s) is/are correct? Select one or more: In pipelining, it is possible that two instructions are fetched in one clock cycle. In pipelining, all parts of the hardware are occupied by different instructions In a 3 stage pipeline, the throughput is 3 instructions per cycle. In ARM Cortex M3, the three phases of instructions executions can be completed in 3 clock cycles for all instructions In a 5 stage pipelining, the instruction latency will be 5 clock cycles. Note Which one(s) is/are correct about ARM Cortex M3 ? (you may choose multiple answers) Select one or more: l-code bus is used to transfer the data to the ARM core processor D-code bus is used for transferring instruction to the ARM core processor D-code bus is 32 bits l-code bus in Cortex M3 is 16 bits Which one(s) is/are not performed in the second cycle of an STR instruction execution? Select one or more: The data transfer takes place The PC is incremented and stored in R15 PC is fed back into the address register The address of the memory where the data is to be stored is sent to the address register Which one(s) are correct about Instruction set architectures? (You may choose multiple answers) Select one or more: In Register-memory, only specific instructions are allowed to get access to memory Register-Register ISA is popular in RISC processors 8086 is an example of a register-register ISA memory-memory is known as load-store architecture Type in the instruction that is used to return from a function

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts