Question: With a resource allocation constrained to two adder and only one divider is available, without multiplier, derive the Verilog design of the (fully dedicated architecture)

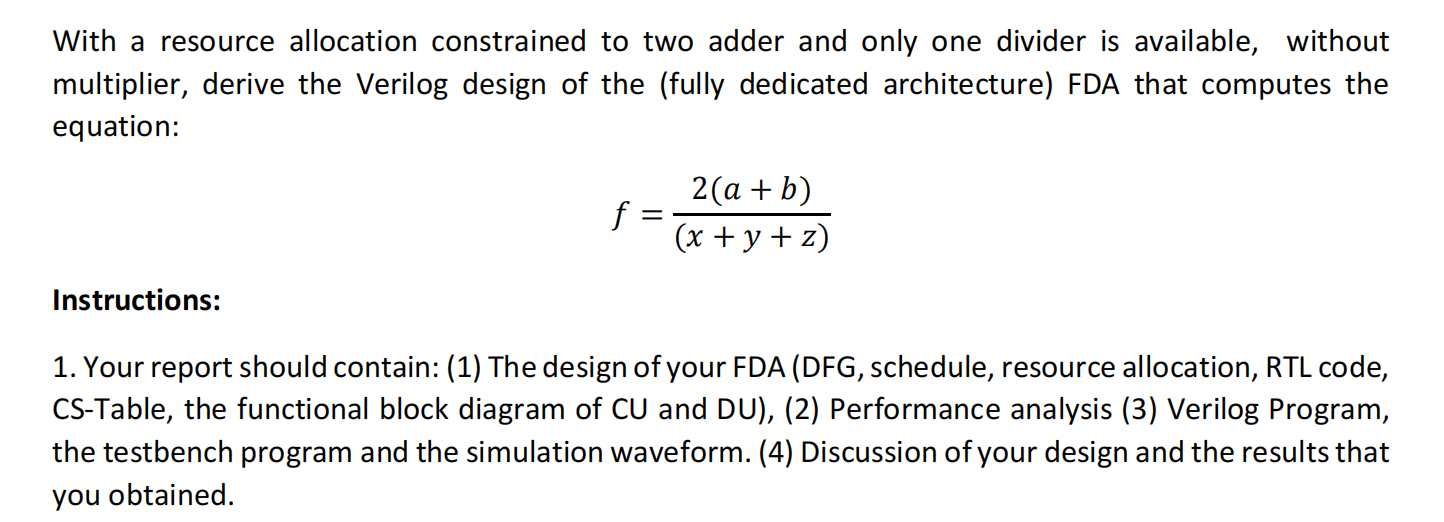

With a resource allocation constrained to two adder and only one divider is available, without multiplier, derive the Verilog design of the (fully dedicated architecture) FDA that computes the equation: 2(a + b) f= (x + y + z) Instructions: 1. Your report should contain: (1) The design of your FDA (DFG, schedule, resource allocation, RTL code, CS-Table, the functional block diagram of CU and DU), (2) Performance analysis (3) Verilog Program, the testbench program and the simulation waveform. (4) Discussion of your design and the results that you obtained

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts