Question: Write a Self - Diagnosis ( Built - in self - test ) test - bench that is able to exhaustively tests the 4 -

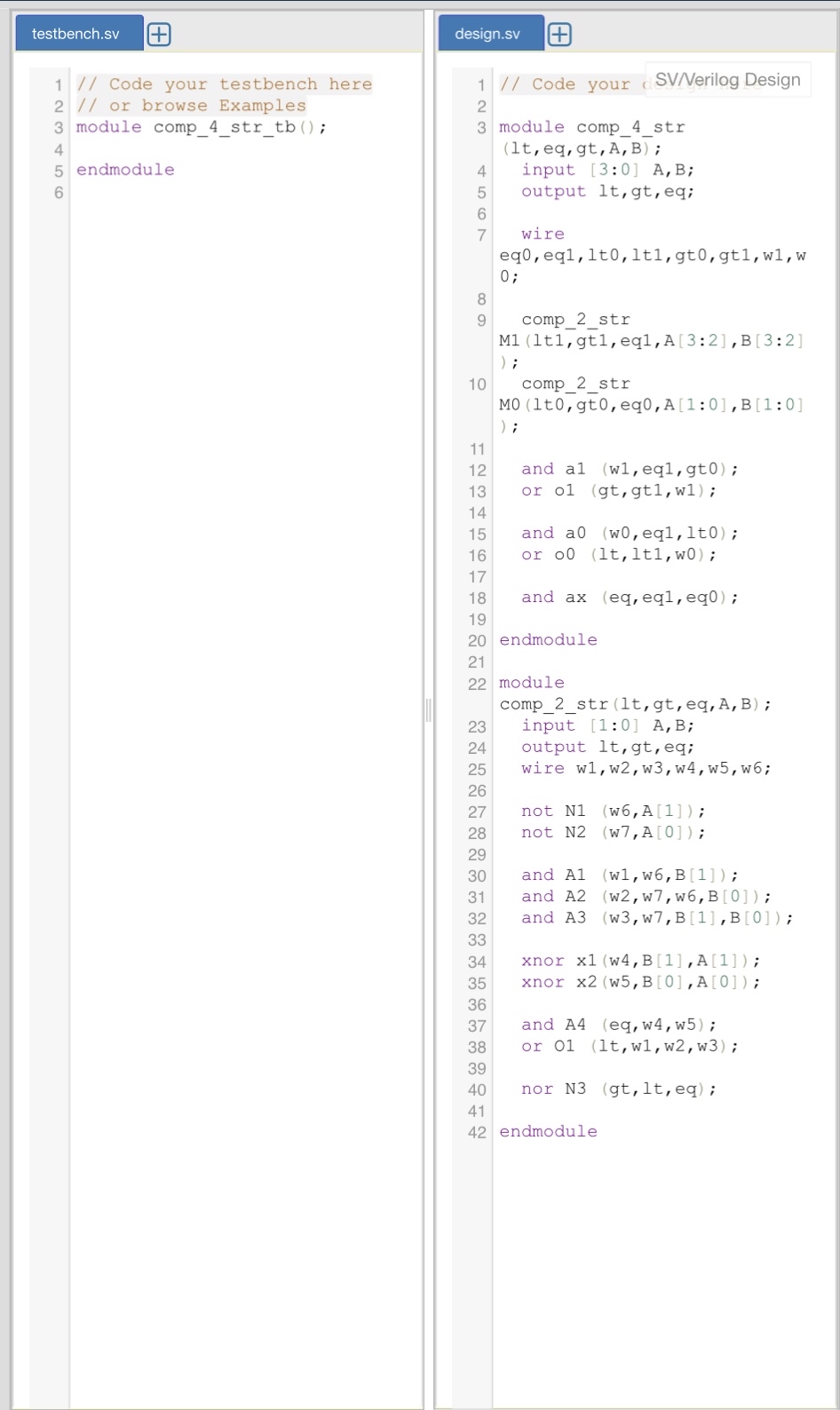

Write a SelfDiagnosis Builtin selftest testbench that is able to exhaustively tests the bit comparator. testbench.sv

Code your testbench here

or browse Examples

module compstrtb;

endmodule

design.sv

Code your SVVerilog Design

module compstr

lt eq gt A B;

input :;

output lt gt eq;

wire

eq eq lto, lt gt gtww

;

compstr

Mt gt eq A : B :

;

compstr

Mt gto, eq A : B :

;

and aw eq gt;

or ol gtgtw;

and aw eq lto;

or ;

and ax eq eq eq;

endmodule

module

compstrt gt eq A B ;

input :;

output lt gt eq;

wire w www w w;

not ;

not NwA;

and Aw w B;

and AwwwB;

and w w B B;

xnor ;

xnor ;

and Aeqww;

or ltwww;

nor Ngt lt eq;

endmoduleExhaustively compares the actual output of the module with the expected output for every test case andmessages the pass and failure of any test case.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock