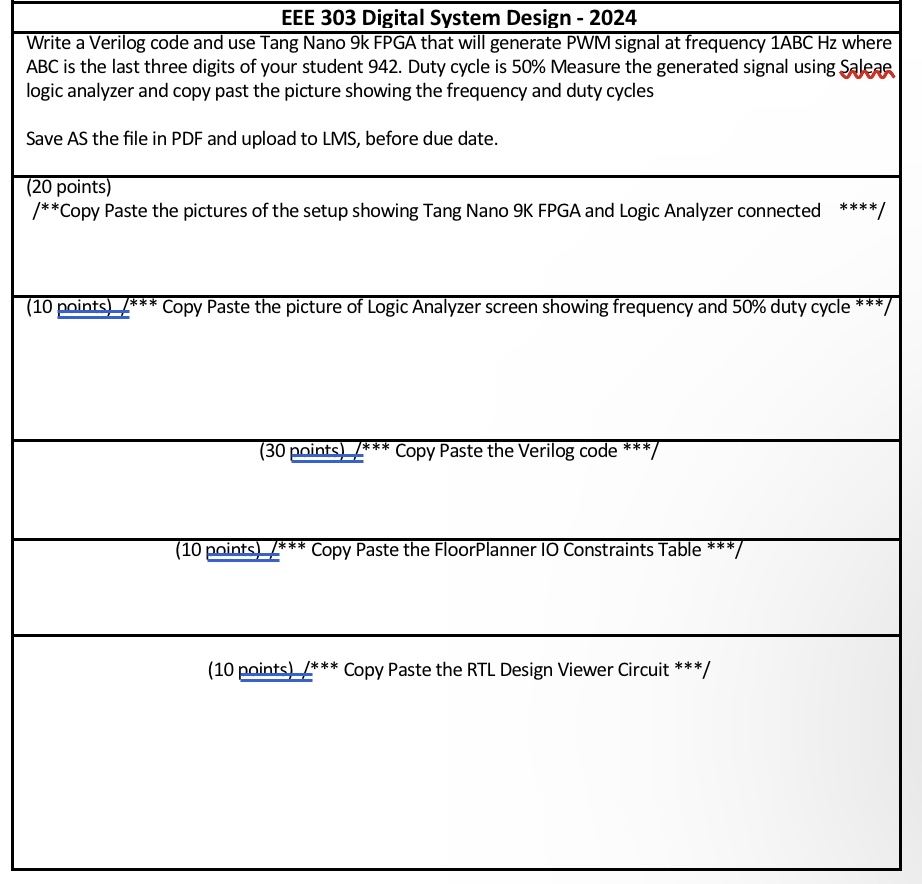

Question: Write a Verilog code and use Tang Nano 9 k FPGA that will generate PWM signal at frequency 1 ABC Hz whereABC is the last

Write a Verilog code and use Tang Nano k FPGA that will generate PWM signal at frequency ABC Hz whereABC is the last three digits of your student Duty cycle is Measure the generated signal using Saleae logic analyzer and copy past the picture showing the frequency and duty cycles

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock