Question: Write a Verilog module which accepts the clock, a reset, the immediate value from the instruction word (least significant byte), and the zero output from

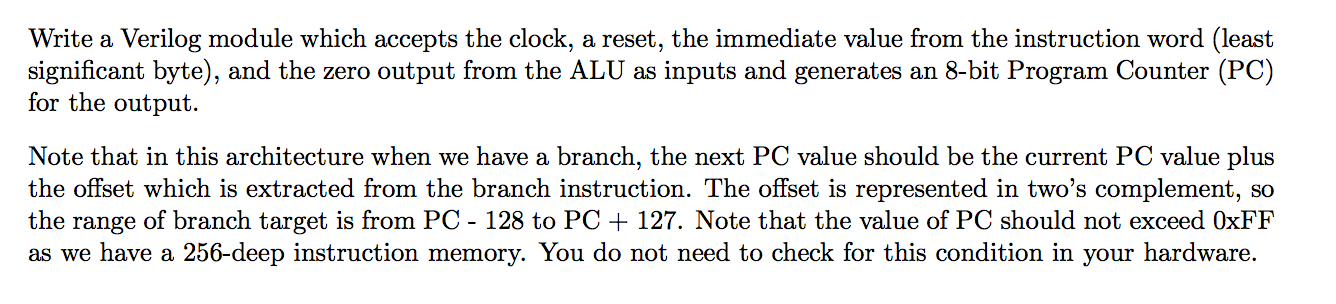

Write a Verilog module which accepts the clock, a reset, the immediate value from the instruction word (least significant byte), and the zero output from the ALU as inputs and generates an 8-bit Program Counter (PC) for the output. Note that in this architecture when we have a branch, the next PC value should be the current PC value plus the offset which is extracted from the branch instruction. The offset is represented in two's complement, so the range of branch target is from PC - 128 to PC + 127. Note that the value of PC should not exceed 0xFF as we have a 256-deep instruction memory. You do not need to check for this condition in your hardware

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts