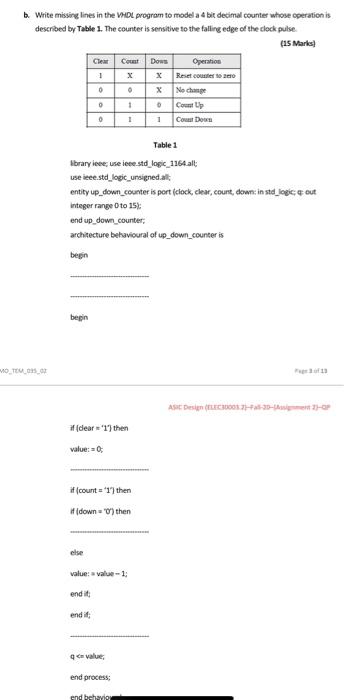

Question: Write missing lines in the VHDL program to model a4 bit decimal counter whose operation is described by Table 1. The counter is sensitive to

Write missing lines in the VHDL program to model a4 bit decimal counter whose operation is described by Table 1. The counter is sensitive to the falling edge of the clock pulse. (15 Marks! Count Dows Operation X Reset counter too X Noche 1 0 Comp 0 1 Cow Down Table 1 Ibrary ieee use eestd_logic_1164. alt use ieee.std_logic_unsigned all entity up_down_counter is port (clock, clear,count, down: in std_logout Integer range Oto 15: end up_down_counter architecture behavioural of up_down_counter is begin begin At Design (ECO-5-3 --- ideare'1') then value: = 0; if (count='1') then down-'0') then else value:value-1: endit endit value end process: end behavior

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts