Question: Write the VERILOG code to implement the following Finite State Machine. This FSM has four states: St0, St1, St2, and St3. There are three inputs:

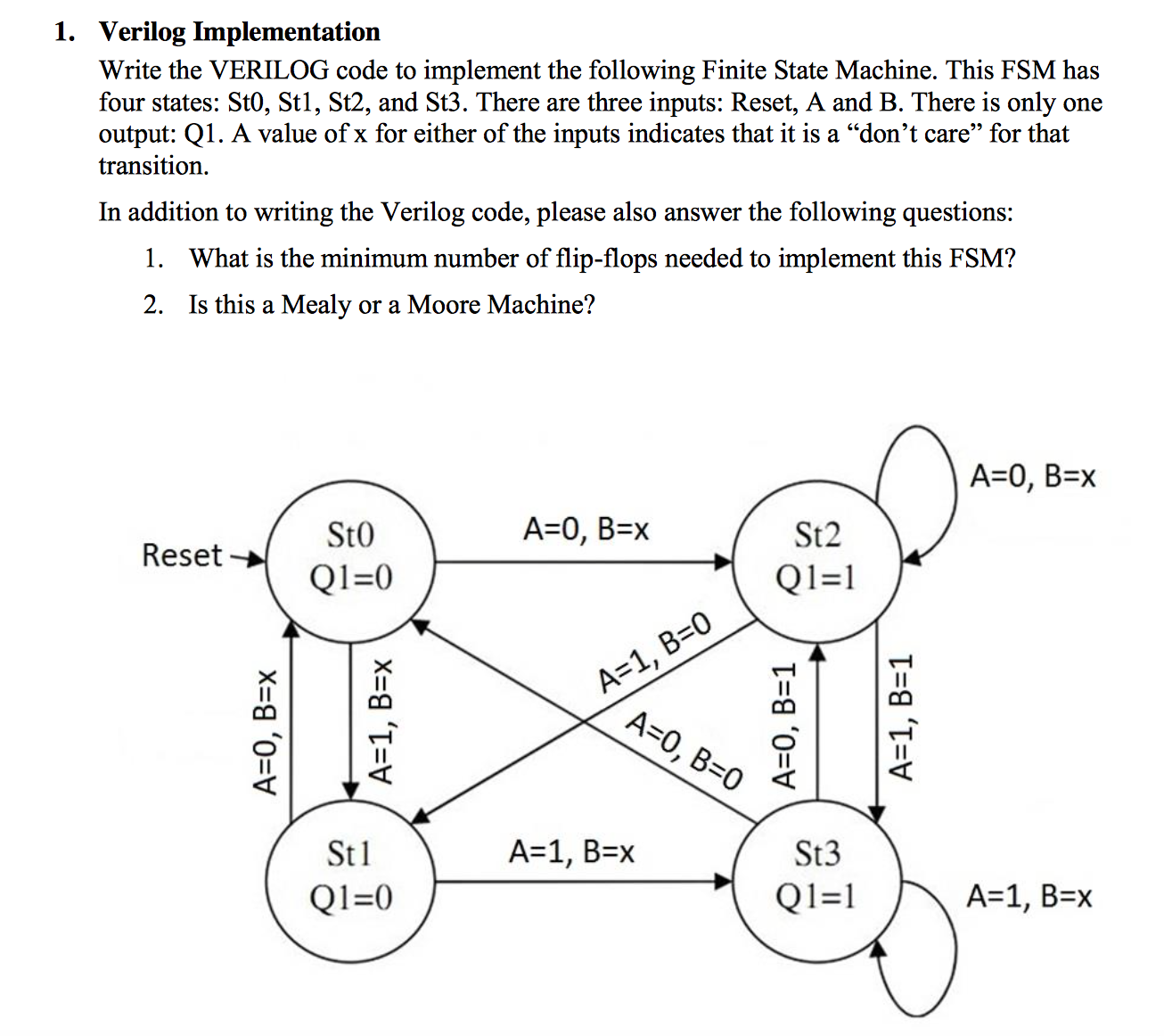

Write the VERILOG code to implement the following Finite State Machine. This FSM has four states: St0, St1, St2, and St3. There are three inputs: Reset, A and B. There is only one output: Q1. A value of x for either of the inputs indicates that it is a dont care for that transition.

In addition to writing the Verilog code, please also answer the following questions:

What is the minimum number of flip-flops needed to implement this FSM?

Is this a Mealy or a Moore Machine?

1. Verilog Implementation Write the VERILOG code to implement the following Finite State Machine. This FSM has four states: St0, Stl, St2, and St3. There are three inputs: Reset, A and B. There is only one output: Q1. A value of x for either of the inputs indicates that it is a "don't care" for that transition,. In addition to writing the Verilog code, please also answer the following questions: What is the minimum number of flip-flops needed to implement this FSM? Is this a Mealy or a Moore Machine? 1. 2. A=0, B=x A 0, B x St0 Q1-0 St2 QI=1 Reset Stl QI=0 St3 QI=1 A-1, B-x A-1, B=x

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts