Question: Write VHDL/ Verilog code for an ALU circuit (as discussed in class) shown below. You can make the top-level module either behavioral or structural. Write

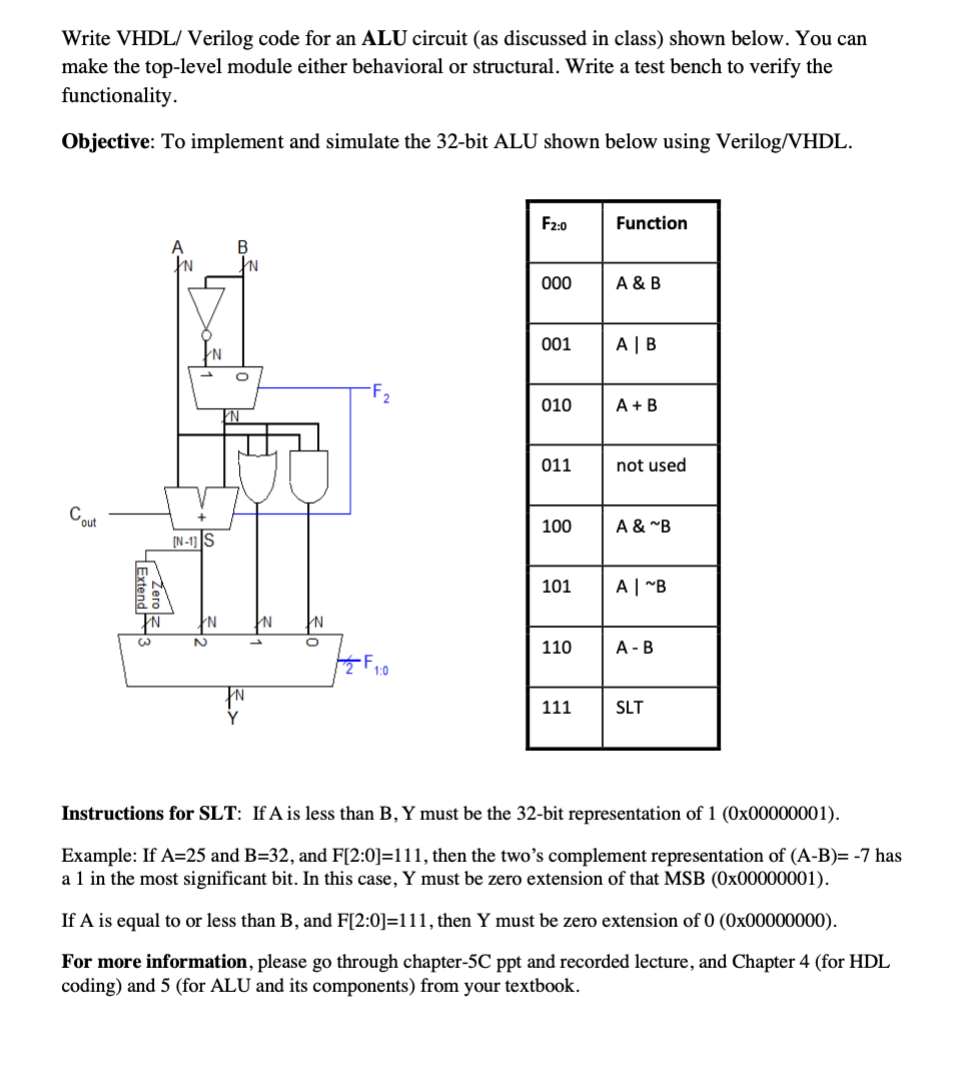

Write VHDL/ Verilog code for an ALU circuit (as discussed in class) shown below. You can make the top-level module either behavioral or structural. Write a test bench to verify the functionality. Objective: To implement and simulate the 32-bit ALU shown below using Verilog/VHDL. Instructions for SLT: If A is less than B,Y must be the 32-bit representation of 1 (0x00000001). Example: If A=25 and B=32, and F[2:0]=111, then the two's complement representation of (AB)=7 has a 1 in the most significant bit. In this case, Y must be zero extension of that MSB (0x00000001). If A is equal to or less than B, and F[2:0]=111, then Y must be zero extension of 0(000000000). For more information, please go through chapter-5C ppt and recorded lecture, and Chapter 4 (for HDL coding) and 5 (for ALU and its components) from your textbook

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts