Question: You would like to instantiate an SRAM array that has 1024 entries of 8 bits. Assume an SRAM cell is 0.25Alm high and 1 Aum

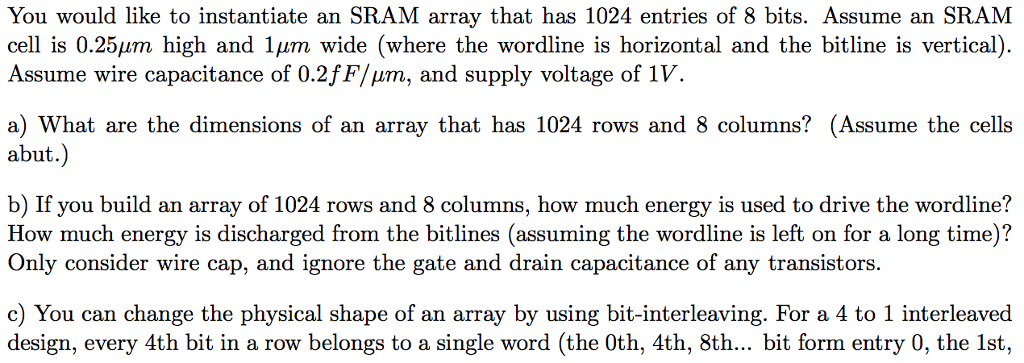

You would like to instantiate an SRAM array that has 1024 entries of 8 bits. Assume an SRAM cell is 0.25Alm high and 1 Aum wide (where the wordline is horizontal and the bitline is vertical). Assume wire capacitance of 0.2fF/Aum, and supply voltage of 1V. a) What are the dimensions of an array that has 1024 rows and 8 columns (Assume the cells abut.) b) If you build an array of 1024 rows and 8 columns, how much energy is used to drive the wordline? How much energy is discharged from the bitlines (assuming the wordline is left on for a long time? Only consider wire cap, and ignore the gate and drain capacitance of any transistors c You can change the physical shape of an array by using bit-interleaving. For a 4 to 1 interleaved design, every 4th bit in a row belongs to a single word (the 0th, 4th, 8th... bit form entry 0, the 1st

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts