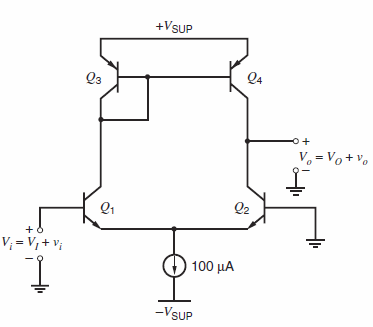

Question: Determine the worst-case input offset voltage for the circuit of Fig. 4.58. Assume the worst-case I S mismatches in the transistors are ± 5 percent

Fig. 4.58:

+VSUP Q4 Q3 V, = Vo+v, Q2 +6 V; = V, + v; 100 -VSUP

Step by Step Solution

3.33 Rating (159 Votes )

There are 3 Steps involved in it

From 4315 Wor... View full answer

Get step-by-step solutions from verified subject matter experts

Document Format (2 attachments)

1528_605d88e1b07d0_686850.pdf

180 KBs PDF File

1528_605d88e1b07d0_686850.docx

120 KBs Word File