Question: How many register read ports should the processor have to avoid any resource hazards due to register reads? This exercise explores how branch prediction affects

How many register read ports should the processor have to avoid any resource hazards due to register reads?

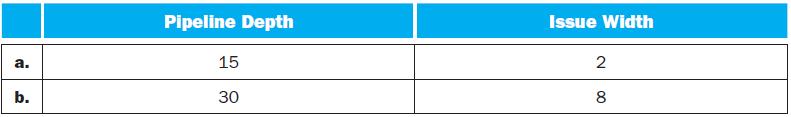

This exercise explores how branch prediction affects performance of a deeply pipelined multiple-issue processor. Problems in this exercise refer to a processor with the following number of pipeline stages and instructions issued per cycle:

a. b. Pipeline Depth 15 30 Issue Width 2 8

Step by Step Solution

3.24 Rating (159 Votes )

There are 3 Steps involved in it

Through adding additional hardware we can implement two read ports as well as a write port to the Re... View full answer

Get step-by-step solutions from verified subject matter experts