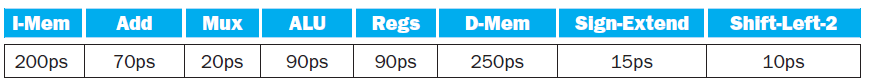

Question: Problems in this exercise assume that logic blocks needed to implement a processors datapath have the following latencies: 1. If the only thing we need

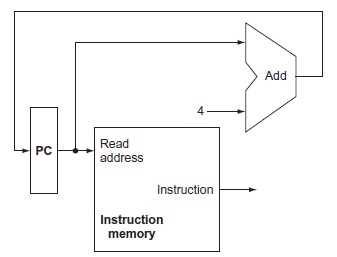

1. If the only thing we need to do in a processor is fetch consecutive instructions (Figure 4.6), what would the cycle time be?

Figure 4.6

2. Consider a datapath similar to the one in Figure 4.11, but for a processor that only has one type of instruction: unconditional PC-relative branch. What would the cycle time be for this datapath?

3. Repeat 4.4.2, but this time we need to support only conditional PC-relative branches. The remaining three problems in this exercise refer to the datapath element Shift - left -2:

4. Which kinds of instructions require this resource?

5. For which kinds of instructions (if any) is this resource on the critical path?

6. Assuming that we only support beq and add instructions, discuss how changes in the given latency of this resource affect the cycle time of the processor. Assume that the latencies of other resources do not change.

Add Sign-Extend I-Mem Mux ALU Regs D-Mem Shift-Left-2 200ps 70ps 20ps 90ps 250ps 15ps 10ps 90ps Add Read PC address Instruction Instruction memory

Step by Step Solution

3.31 Rating (157 Votes )

There are 3 Steps involved in it

1 IMem takes longer than the Add unit so the clock cycle time is equal to the latency of the IMem 200 ps 2 Th e critical path for this instruction is ... View full answer

Get step-by-step solutions from verified subject matter experts