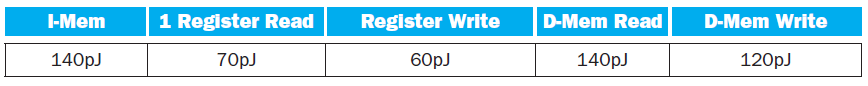

Question: This exercise explores energy efficiency and its relationship with performance. Problems in this exercise assume the following energy consumption for activity in Instruction memory, Registers,

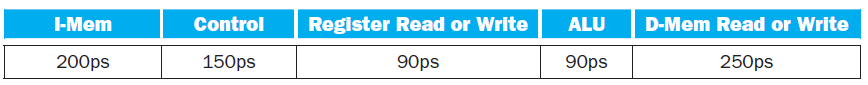

Assume that components in the datapath have the following latencies. You can assume that the other components of the datapath have negligible latencies.

1. How much energy is spent to execute an ADD instruction in a single-cycle design and in the 5-stage pipelined design?

2. What is the worst-case MIPS instruction in terms of energy consumption, and what is the energy spent to execute it?

3. If energy reduction is paramount, how would you change the pipelined design? What is the percentage reduction in the energy spent by an LW instruction aft er this change?

4. What is the performance impact of your changes from 4.19.3?

5. We can eliminate the MemRead control signal and have the data memory be read in every cycle, i.e., we can permanently have MemRead=1. Explain why the processor still functions correctly aft er this change. What is the effect of this change on clock frequency and energy consumption?

1 Register Read Register Write I-Mem D-Mem Read D-Mem Write 140pJ 120pJ 140pJ 70pJ 60pJ Control Register Read or Write D-Mem Read or Write I-Mem ALU 200ps 150ps 90ps 90ps 250ps

Step by Step Solution

3.40 Rating (166 Votes )

There are 3 Steps involved in it

1 The energy for the two designs is the same IMem is read two registers are read and a register is written We have 140 pJ 270 ps 60 pJ 340 pJ 2 The in... View full answer

Get step-by-step solutions from verified subject matter experts