Repeat 4.19.3 but this time determine which of the two options results in shorter time per instruction.

Question:

Repeat 4.19.3 but this time determine which of the two options results in shorter time per instruction.

Problem 4.19.3

Let us assume that we cannot afford to have three-input Muxes that are needed for full forwarding. We have to decide if it is better to forward only from the EX/MEM pipeline register (next-cycle forwarding) or only from the MEM/WB pipeline register (two-cycle forwarding). Which of the two options results in fewer data stall cycles?

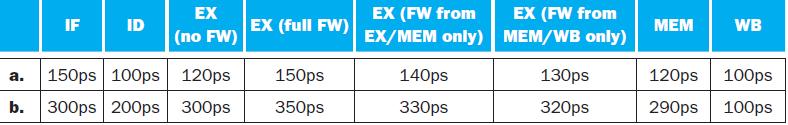

The remaining three problems in this exercise refer to the following latencies for individual pipeline stages. For the EX stage, latencies are given separately for a processor without forwarding and for a processor with different kinds of forwarding.

Step by Step Answer:

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy