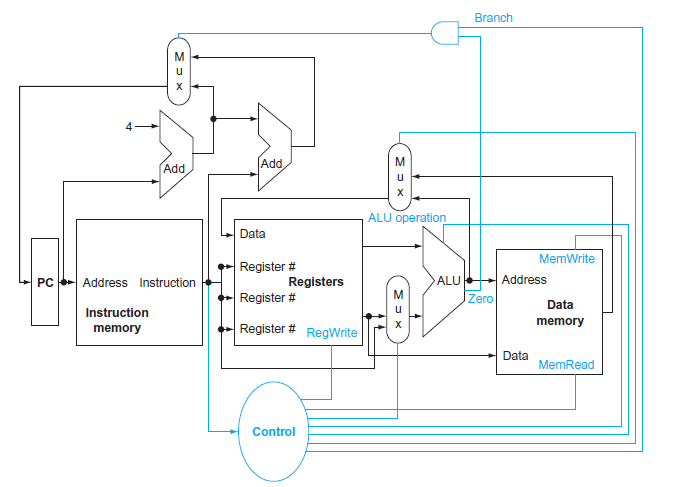

Question: The basic single-cycle MIPS implementation in Figure 4.2 can only implement some instructions. New instructions can be added to an existing Instruction Set Architecture (ISA),

Instruction: LWI Rt,Rd(Rs)

Interpretation: Reg[Rt] = Mem[Reg[Rd]+Reg[Rs]]

Figure 4.2

1. Which existing blocks (if any) can be used for this instruction?

2. Which new functional blocks (if any) do we need for this instruction?

3. What new signals do we need (if any) from the control unit to support this instruction?

Branch Add Add ALU operation Data MemWrite Register # Address ALU Registers PC Address Instruction IZero Register # Data Instruction memory Register # RegWrite memory Data MemRead Control

Step by Step Solution

3.45 Rating (168 Votes )

There are 3 Steps involved in it

1 This instruction uses instruction memory both register read port... View full answer

Get step-by-step solutions from verified subject matter experts