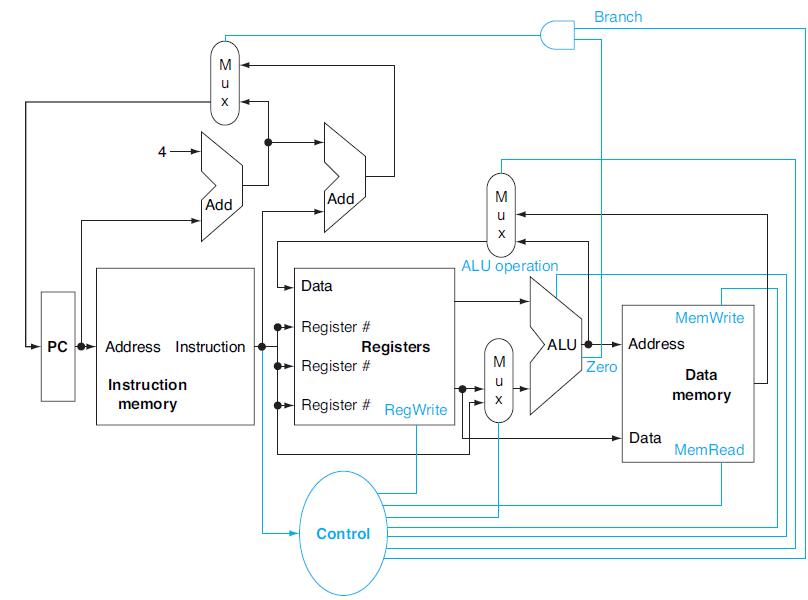

Question: What new signals do we need (if any) from the control unit to support this instruction? The basic single-cycle MIPS implementation in Figure 4.2 can

What new signals do we need (if any) from the control unit to support this instruction?

The basic single-cycle MIPS implementation in Figure 4.2 can only implement some instructions. New instructions can be added to an existing ISA, but the decision whether or not to do that depends, among other things, on the cost and complexity such an addition introduces into the processor datapath and control. The first three problems in this exercise refer to this new instruction:![a. b. Instruction SEQ Rd, Rs. Rt LWI Rt, Rd (Rs) Reg[Rd] Reg[Rt] = Interpretation Boolean value (0 or 1) of](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1698/2/1/6/7006538bafd00a0f1698216699865.jpg)

Figure 4.2

a. b. Instruction SEQ Rd, Rs. Rt LWI Rt, Rd (Rs) Reg[Rd] Reg[Rt] = Interpretation Boolean value (0 or 1) of (Reg[Rs] Reg[Rs]) Mem[Reg[Rd]+Reg[Rs ]]

Step by Step Solution

3.34 Rating (148 Votes )

There are 3 Steps involved in it

To support the new instruction SEQ Rd Rs Rt which computes the logical equality of the values in reg... View full answer

Get step-by-step solutions from verified subject matter experts