Question: Which control signal in Figure 4.24 has the most slack and how much time does the control unit have to generate it if it wants

Which control signal in Figure 4.24 has the most slack and how much time does the control unit have to generate it if it wants to avoid being on the critical path?![PC Instruction [25-0] Add Read address Instruction [31-0] Instruction memory 26 Shift left 2/ Instruction](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1698/2/2/3/2746538d4aab98951698223272879.jpg)

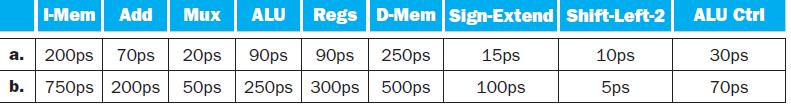

In this exercise we examine how the clock cycle time of the processor affects the design of the control unit, and vice versa. Problems in this exercise assume that the logic blocks used to implement the datapath have the following latencies:

PC Instruction [25-0] Add Read address Instruction [31-0] Instruction memory 26 Shift left 2/ Instruction [31-26] Instruction [25-21] Instruction [20-16] Instruction [15-11] Instruction [15-0] Jump address [31-0] PC +4 [31-28] Control XENO 28 RegDst Jump Branch MemRead MemtoReg ALUOD MemWrite ALUSrc RegWrite Read register 1 Read register 2 Read 16 data 1 Write Read register data 2 Write data Registers Sign- extend 32 Instruction [5-0] Shift left 2, XESO Add ALU result Zero ALU ALU result ALU control/ Address (o Ex- 0 1 Read data Write Data data memory MUX MUX

Step by Step Solution

3.40 Rating (156 Votes )

There are 3 Steps involved in it

We must locate the critical path in the processors datapath in order to ascertain which control sign... View full answer

Get step-by-step solutions from verified subject matter experts