Question: Give an example that uses delayed branch with the three-segment pipeline of Sec. 9-5. Example: Three-Segment Instruction Pipeline A typical set of instructions for a

Give an example that uses delayed branch with the three-segment pipeline of Sec. 9-5.

![Delayed Load Consider now the operation of the following four instructions: 1. LOAD: R1M[address 1]](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1698/0/6/5/80565366d8d74a68image_%282%29.png)

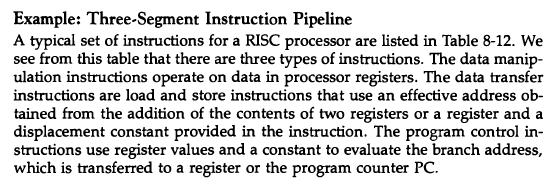

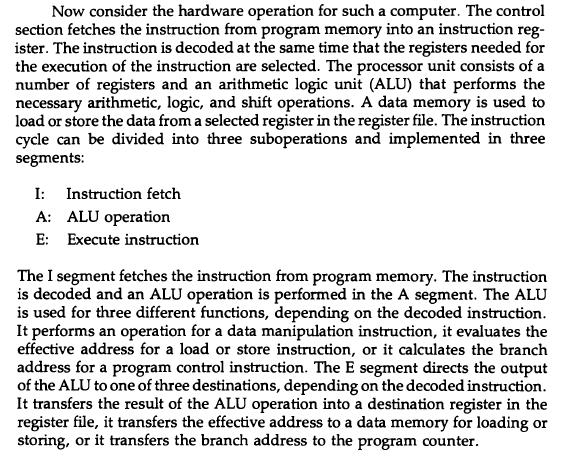

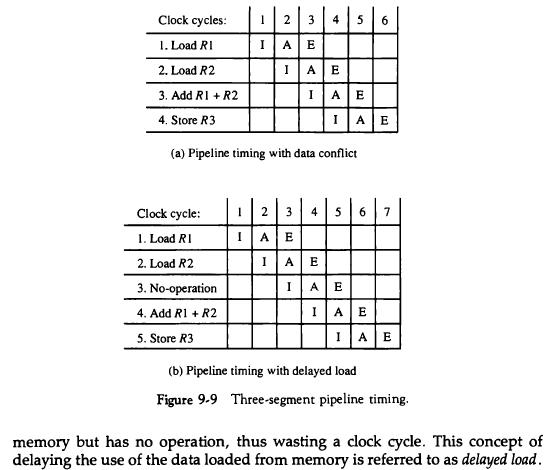

Example: Three-Segment Instruction Pipeline A typical set of instructions for a RISC processor are listed in Table 8-12. We see from this table that there are three types of instructions. The data manip- ulation instructions operate on data in processor registers. The data transfer instructions are load and store instructions that use an effective address ob- tained from the addition of the contents of two registers or a register and a displacement constant provided in the instruction. The program control in- structions use register values and a constant to evaluate the branch address, which is transferred to a register or the program counter PC.

Step by Step Solution

3.45 Rating (165 Votes )

There are 3 Steps involved in it

The provided text describes a threesegment instruction pipeline in the context of a RISC processor and discusses the issue of data conflicts particula... View full answer

Get step-by-step solutions from verified subject matter experts