Question: Write an HDL module for the Gray code counter from Exercise 3.27.? Data from problem 3.27 Gray codes have a useful property in that consecutive

Write an HDL module for the Gray code counter from Exercise 3.27.?

Data from problem 3.27

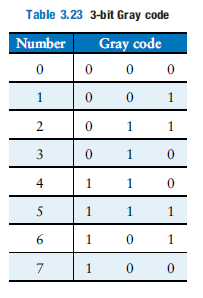

Gray codes have a useful property in that consecutive numbers differ in only a single bit position. Table 3.23 lists a 3-bit Gray code representing the numbers 0 to 7. Design a 3-bit modulo 8 Gray code counter FSM with no inputs and three outputs. (A modulo N counter counts from 0 to N ? 1, then

repeats. For example, a watch uses a modulo 60 counter for the minutes and seconds that counts from 0 to 59.) When reset, the output should be 000. On each clock edge, the output should advance to the next Gray code. After reaching 100, it should repeat with 000.

Table 3.23 3-bit Gray code Number Gray code 0 0 1 1 1 1 4 5 1 6 1 7 1 0 0 2. 3.

Step by Step Solution

3.42 Rating (158 Votes )

There are 3 Steps involved in it

SystemVerilog VHDL module ex4 37 input logic output t... View full answer

Get step-by-step solutions from verified subject matter experts