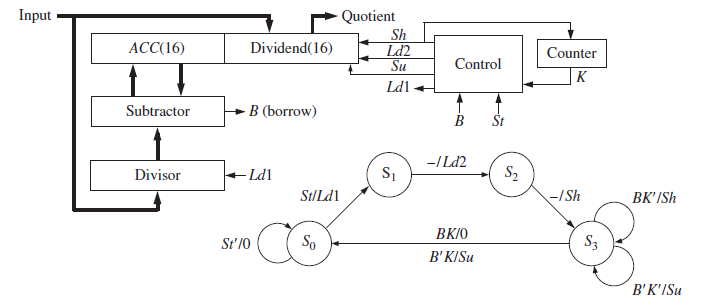

Question: A block diagram and state graph for a divider for unsigned binary numbers is shown subsequently. This divider divides a 16-bit dividend by a 16-bit

Input Quotient Sh Ld2 Su ACC(16) Dividend(16) Counter Control K Ld1 B (borrow) Subtractor t -IL42 S2 Ld1 Divisor -/Sh St/Ld1 BK'ISh BK/0 So S3 St'/0 B' KISU B'K'ISu

Step by Step Solution

3.48 Rating (164 Votes )

There are 3 Steps involved in it

module dividerSt clk Input Quotient input St clk input 150 Input output 150 Qu... View full answer

Get step-by-step solutions from verified subject matter experts