(a) If logic blocks of Figure 6-1(a) are used, how many LUTs are required to build a...

Question:

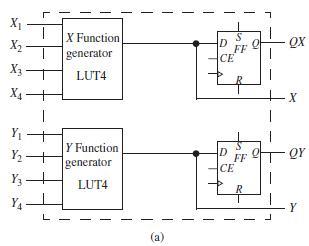

(a) If logic blocks of Figure 6-1(a) are used, how many LUTs are required to build a 4-bit adder with accumulator?

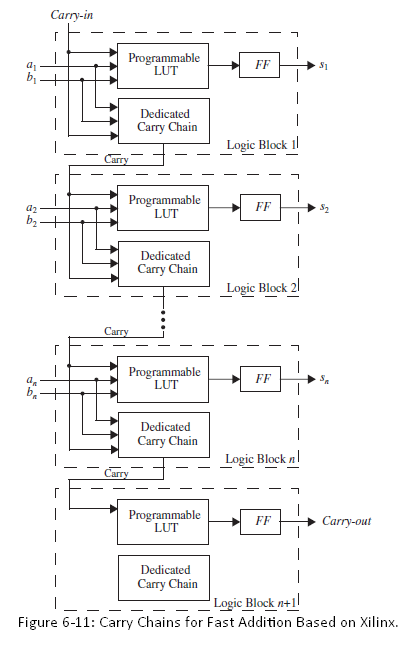

(b) If an FPGA with built-in carry-chain logic as shown in Figure 6-11 is used, how many 4-input LUTs are required?

(c) Design a 4-bit adder-subtracter with accumulator using an FPGA with carry-chain logic and 4-input LUTs. Assume a control signal Su which is 0 for addition and 1 for subtraction. Show the required connections on a diagram similar to that shown in Figure 6-11 and give the function realized by each LUT.

Figure 6-1(a)

Figure 6-11

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted: