Question: A 4 4 array multiplier (Figure 4-29) is to be implemented using an FPGA. (a) Partition the logic so that it fits in a

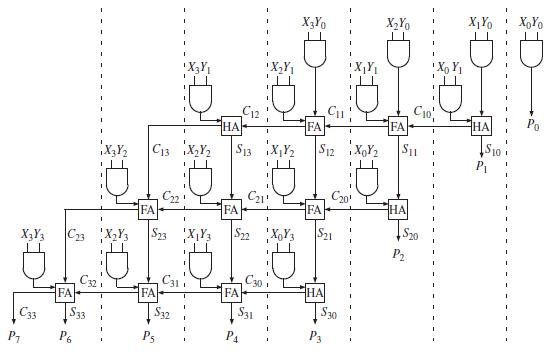

A 4 ⊗ 4 array multiplier (Figure 4-29) is to be implemented using an FPGA.

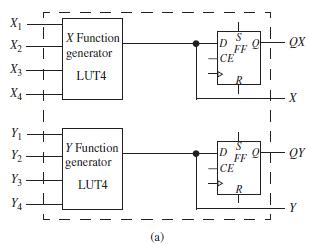

(a) Partition the logic so that it fits in a minimum number of Figure 6-1(a) logic blocks. Draw loops around each set of components that will fit in a single logic block. Determine the total number of 4-input LUTs required.

(b) Repeat part (a), except assume that carry-chain logic is available.

Figure 4-29

Figure 6.1(a)

,Y XY0 Yo X,Y0 ' Xo Y1 'X31 'X,Y1 :X,, ; FA C12 ; FA Po ,Y, S12 XQY2 | , S13 X,Y2 P1 FA C22 FA C21 FA Sza X,Y Sz2 XoY |C23 X,Y3 S21 S20 X P2 FA FA ! FA S33 S32 S31 S30 P7 P4 FIGURE 4-29

Step by Step Solution

3.43 Rating (156 Votes )

There are 3 Steps involved in it

a 14 cells total b 14 cells total 6 for adders and 8 f... View full answer

Get step-by-step solutions from verified subject matter experts