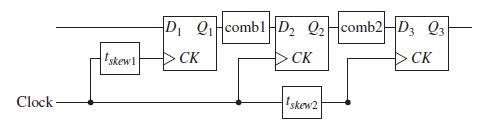

Question: Consider the following circuit where the combinational circuit is represented by COMB and clock skew is represented by t skew . Given the following parameters:

Consider the following circuit where the combinational circuit is represented by COMB and clock skew is represented by tskew.

Given the following parameters:

FF setup time = 20 ns

FF hold time = 10 ns

FF propagation delay = 5 to 10 ns

Tcomb 1 = 5 ns to 7 ns

Tcomb 2 = 6 ns to 11 ns

(a) What is the minimum clock period with tskew1 = tskew2 = 0?

(b) Now set Tcomb1 = 1 to 4 ns. Is there a setup time violation for the middle flip-flop? If no, what is the setup time margin?

(c) Now set Tcomb1 = 1 to 4 ns. Is there a hold-time violation for the middle flip-flop? If no, what is the hold-time margin?

(d) What are the minimum values of tskew1 and tskew2 that will fix the violations?

(e) What is the minimum clock period after violations have been fixed?

D, QHcomb1-D2 Q2Hcomb2D3 Q3 skew1 >CK CK >CK Clock - fskew2

Step by Step Solution

3.43 Rating (166 Votes )

There are 3 Steps involved in it

a Consider following delays input to first FF t su 20 ns left FF to middle FF t pmax t c1... View full answer

Get step-by-step solutions from verified subject matter experts