Question: Modify the nonretriggerable, level-sensitive, one-shot design example from either Figure 7-95 (AHDL) or Figure 7-96 (VHDL) so that the one-shot is retriggerable but still level-sensitive.

Modify the nonretriggerable, level-sensitive, one-shot design example from either Figure 7-95 (AHDL) or Figure 7-96 (VHDL) so that the one-shot is retriggerable but still level-sensitive. Simulate the design.

Figure 7-95

![12345 6 7 8 9 SUBDESIGN fig7_95 ( ) clock, trigger, reset delay [3..0] q VARIABLE count [3..0] BEGIN 10 11 12](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/9/6/3/7886553638c8cef91699963788806.jpg)

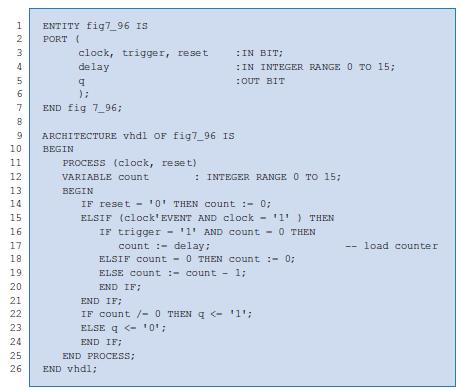

Figure 7-96

12345 6 7 8 9 SUBDESIGN fig7_95 ( ) clock, trigger, reset delay [3..0] q VARIABLE count [3..0] BEGIN 10 11 12 13. 14 15 16 17 18 END; : DFF; count[].clk - clock; count[].clrn - reset; IF trigger & count [].qb"0000" THEN count[].d delay []; : INPUT; : INPUT; : OUTPUT: ELSIF count[].qB"0000" THEN count[].d - B"0000"; ELSE count[].d count[].q- 1; END IF; q count[].q - B"0000"; -- make output pulse

Step by Step Solution

3.48 Rating (165 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts