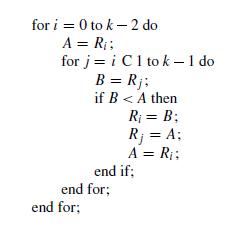

Question: Figure 7.40 gives pseudo-code for the sorting operation in which the registers being sorted are indexed using variables i and j. In the ASM chart

Figure 7.40 gives pseudo-code for the sorting operation in which the registers being sorted are indexed using variables i and j. In the ASM chart in Figure 7.41, variables i and j are implemented using the counters Ci and Cj . A different approach is to implement i and j using two shift registers.

(a) Redesign the circuit for the sorting operation using the shift registers instead of the counters to index registers R0, . . . , R3.

(b) Give Verilog code for the circuit designed in part (a).

(c) Discuss the relative merits and drawbacks of your circuit in comparison with the circuit that uses the counters Ci and Cj .

for i = 0 to k-2 do A = R; for ji C1 to k - 1 do B = Rj; if B < A then end for; end for; R = B; Rj = A; A = R: end if;

Step by Step Solution

3.46 Rating (182 Votes )

There are 3 Steps involved in it

a Redesign the circuit for the sorting operation using the shift registers instead of the counters t... View full answer

Get step-by-step solutions from verified subject matter experts