A new instruction, SMR (Store Multiple Registers), with symbolic opcode name SMR, is to be implemented for

Question:

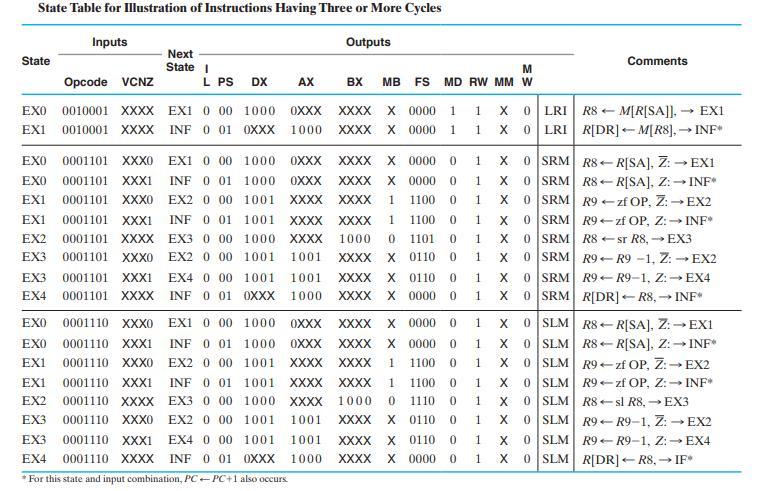

A new instruction, SMR (Store Multiple Registers), with symbolic opcode name SMR, is to be implemented for the multiple- cycle computer. The instruction stores the contents of eight registers in eight consecutive memory locations. Register R[SA] specifies the address in memory M to which the first register R[SB] is to be stored. The registers to be stored are R[SB], R[(SB+1)

modulo 8], . . ., R[(SB+7)modulo 8] in Memory M addresses R[SA], R[SA] +1, . . ., R[SA]+7. Design this instruction presenting your final results in the form shown in Table 8-15.

Table 8-15.

Transcribed Image Text:

State Table for Illustration of Instructions Having Three or More Cycles Inputs State Next State I L PS DX Outputs Opcode VCNZ EXO 0010001 XXXX EX1 0 00 1000 0XXX XXXX X 0000 1 1 X EX1 0010001 XXXX INF 0 01 0XXX 1000 XXXX X 0000 1 1 AX M BX MB FS MD RW MM W 0 0 EXO 0001101 XXXO EX1 0 00 1000 0XXX XXXX X 0000 EXO 0001101 XXXI INF 0 01 1000 0XXX XXXX X 0000 EX1 0001101 XXXO EX2 0 00 1001 XXXX XXXX 1 1100 EX1 0001101 XXX1 INF 0 01 1001 XXXX XXXX 1 1100 EX2 0001101 XXXX EX3 0 00 1000 XXXX 1000 0 1101 0 EX3 0001101 XXX0 EX2 0 00 1001 1001 XXXX X 0110- 0 EX3 0001101 XXXI EX4 0 00 1001 1001 XXXX X 0110 0 1 EX4 0001101 XXXX INF 0 01 0XXX 1000 XXXX X 0000 0 1 EXO 0001110 XXXO EX1 0 00 1000 0XXX XXXX X 0000 0 EXO 0001110 XXX1 INF 0 01 1000 0XXX XXXX X 0000 0 EX1 0001110 XXXO EX2 0 00 1001 XXXX XXXX 1 1100 0 EX1 0001110 XXX1 INF 0 01 1001 XXXX XXXX 1 1100 0 EX2 0001110 XXXX EX3 0 00 1000 XXXX 1000 0 1110 0 EX3 0001110 XXX0 EX2 0 00 1001 1001 XXXX X 0110 0 EX3 0001110 XXX1 EX4 0 00 1001 1001 XXXX X 0110 0 EX4 0001110 XXXX INF 0 01 0XXX 1000 XXXX X 0000 0 *For this state and input combination, PC-PC+1 also occurs. 000 0 LRI X 0 LRI 1 X 0 SRM R8 -R[SA], Z: EXI 1 X 0 SRM R8 R[SA], Z: INF* 1 X 0 SRM R9zf OP, Z:-EX2 1 1 1 1 X 0 SRM X 0 SRM 1 1 X 0 SRM 1 1 1 1 1 xxx X X X X X X X X 0 SRM 0 SRM 0 SLM 0 SLM 0 SLM 0 SLM 0 SLM 0 SLM Comments X 0 SLM X 0 SLM R8- - M[R[SA]]. - EX1 R[DR] M[R8], INF* R9-zf OP, Z: INF* R8sr R8,- EX3 R9 R9 -1, Z: -EX2 R9 R9-1, Z: EX4 R[DR] - R8, -> INF* R8- -R[SA], Z: - EX1 R8 R[SA], Z:INF* R9-zf OP, Z: EX2 R9zf OP, Z: INF* R8sl R8. EX3 R9-1, Z: EX2 R9-1, Z: EX4 R9 R9 R[DR] -R8. IF*

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 0% (1 review)

Heres how we can design the SMR instruction implementation 1 Instruction Fetch IF Stage I Instructio...View the full answer

Answered By

Kainat Shabbir

i am an experienced qualified expert with a long record of success helping clients overcome specific difficulties in information technology, business and arts greatly increasing their confidence in these topics. i am providing professional services in following concerns research papers, term papers, dissertation writing, book reports, biography writing, proofreading, editing, article critique, book review, coursework, c++, java, bootstarp, database.

5.00+

184+ Reviews

255+ Question Solved

Related Book For

Logic And Computer Design Fundamentals

ISBN: 9780133760637

5th Edition

Authors: M. Morris Mano, Charles Kime, Tom Martin

Question Posted:

Students also viewed these Computer science questions

-

A new instruction, ANDN (AND NOT), is to be implemented for the multiple-cycle computer. The instruction performs R[DR] = R[SA]^ (NOT(R[SB])). The instruction allows individual bits in register SA to...

-

List the control logic state table entries for the multiple- cycle computer (see Tables 8-12, 8-13 and 8-15) that implement the following register transfer statements. Assume that in all cases the...

-

Grocery Stores Inc. (GSI) is a regional chain of grocery stores operating in southern Ontario. GSI stores are strategically spread throughout the province, outside major metropolitan areas. The great...

-

There are two major producers of corncob pipes in the world. Suppose that the inverse demand function for corncob pipes is described by p = 120 - 4g where g is total industry output and suppose that...

-

In light of your answer to Problem 11.61, explain why one of the following isomers undergoes E2 reaction approximately 100 times as fast as the other. Which isomer is more reactive, andwhy? (a) CI...

-

Internet Magazine monitors Internet service providers (ISPs) and provides statistics on their performance. The average time to download a Web page for free ISPs is approximately 20 seconds for...

-

What account is affected by all prior-period adjustments? On what financial statement are prior-period adjustments reported?

-

One subunit of Zoom Sports Company had the following financial results last month: Requirements 1. Complete the performance evaluation report for the subunit (round to three decimal places). 2. Based...

-

Convergence is O the developing high-quality standards in partnership with national standard-setters. O a synonym for harmonization. the opposite of standardization. O unlike harmonization, takes...

-

A new instruction is to be defined for the multiple- cycle computer. The instruction compares two unsigned integers stored in register R[SA] and R[SB]. If the integers are equal, then bit 0 of R[DR]...

-

In the SRM and SLM instructions, both the operand R[SA] and the shift amount ield OP are checked to see if either is 0 before the shifts begin. (a) Redraw the state machine diagram for these...

-

Piaggio applies overhead to product costs. What account(s) is (are) used to eliminate overapplied or underapplied overhead from the Factory Overhead account, assuming the amount is not material?

-

Salmone Company reported the following purchases and sales of its only product. Salmone uses a perpetual inventory system. Determine the cost assigned to the ending inventory using FIFO. 1 Date...

-

A company may go through organizational change at various stages in its life cycle for a variety of reasons. Reasons can include a change in ownership as well as a change in the competitive...

-

6 (a) Below is a diagram of a rotating disc viscometer (FIGURE 4). Explain its operations and limitations as to use. If, in a similar works situation, it is necessary to make measurements on a...

-

As part of your role in the Business Analytics and Data Analytics team, you have been asked to forecast Food Retailing as part of a wider report being commissioned by the above collaboration - on...

-

You are three students who have together bought a business that makes snow. The customers consist of both large public enterprises and private individuals. The business is run all year round, but the...

-

Consider a hypothetical reaction between A, B, and C that is first order in A, zero order in B, and second order in C. (a) Write the rate law for the reaction. (b) How does the rate change when [A]...

-

Imagine that your best friend knows you are taking a psychology course and wonders what psychology is all about. How would you define psychology for your friend? Write an essay on the discipline of...

-

What is the running time of parenthesize(T, T.root( )), as given in Code Fragment 8.26, for a tree T with n nodes? Fragment 8.26 1 /** Prints parenthesized representation of subtree of T rooted at p....

-

Suppose an initially empty stack S has performed a total of 25 push operations, 12 top operations, and 10 pop operations, 3 of which returned null to indicate an empty stack. What is the current size...

-

Had the stack of the previous problem been an instance of the ArrayStack class, from Code Fragment 6.2, what would be the final value of the instance variable t?

-

Los siguientes datos corresponden a las operaciones de Turk Company el ao pasado: Ventas $ 900 000 Utilidad operativa neta $ 36 000 Margen de contribucin $ 150 000 Activos operativos promedio $ 180...

-

Problem 16-16 Tax Shields (LO2) River Cruises is all-equity-financed with 53,000 shares. It now proposes to issue $280,000 of debt at an interest rate of 12% and to use the proceeds to repurchase...

-

In a process costing system, companies use predetermined overhead rates to apply overhead

Study smarter with the SolutionInn App