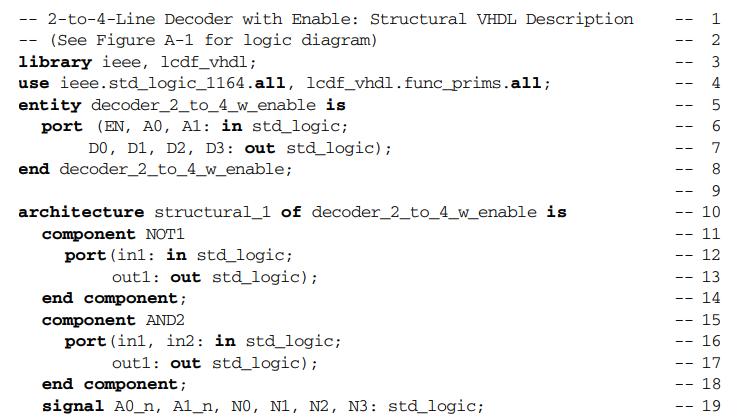

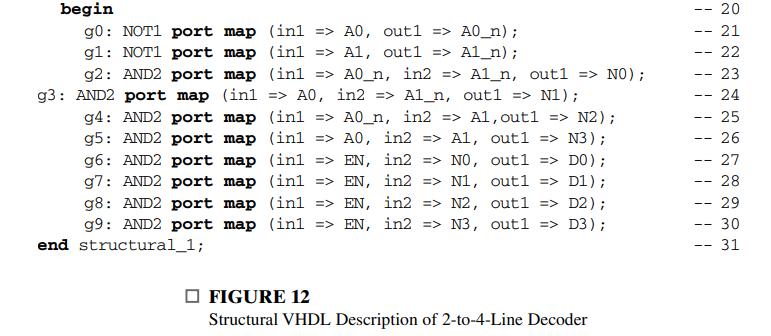

Question: Compile and simulate the 2-to-4-line decoder with enable in Figure 12 for sequence (000,001,010,011,100,101,110,111) on E_n, A0, A1. Verify that the circuit functions as a

Compile and simulate the 2-to-4-line decoder with enable in Figure 12 for sequence \(000,001,010,011,100,101,110,111\) on E_n, A0, A1. Verify that the circuit functions as a decoder. You will need to compile library lcdf_vhdl. func_prims first, since it is used in the simulation.

Data From Figure 12

-- -- 2-to-4-Line Decoder with Enable: Structural VHDL Description (See Figure A-1 for logic diagram) library ieee, lcdf_vhdl; use ieee.std_logic_1164.all, lcdf_vhdl.func_prims.all; entity decoder_2_to_4_w_enable is port (EN, A0, A1: in std_logic; D0, D1, D2, D3: out std_logic); end decoder_2_to_4_w_enable; architecture structural_1 of decoder_2_to_4_w_enable is component NOT1 port (inl: in std_logic; -- -- -- -- -- -- -- 2 12345 6 7 8 -- 9 -- -- 10 11 outl: out std_logic); end component; component AND2 port (in1, in2: in std_logic; outl: out std_logic); end component; signal A0_n, Al_n, NO, N1, N2, N3: std_logic; -- -- -- 12 13 - 14 -- -- -- -- -- 15 16 17 18 19

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts