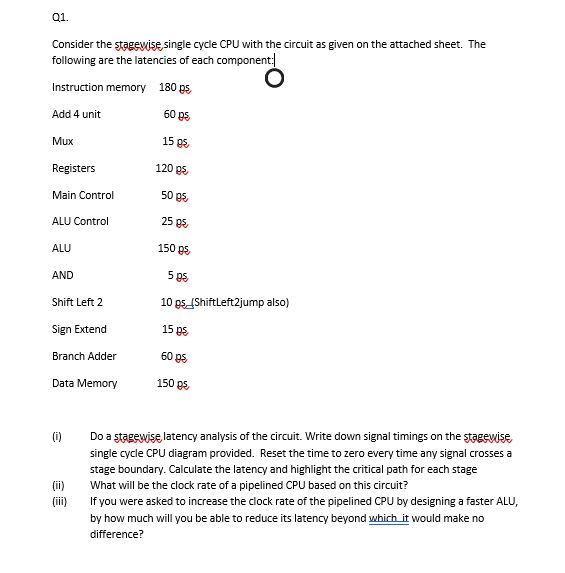

Question: 01. Consider the stagevise single cycle CPU with the circuit as given on the attached sheet. The following are the latencies of each component: Instruction

01. Consider the stagevise single cycle CPU with the circuit as given on the attached sheet. The following are the latencies of each component: Instruction memory 180 ps Add 4 unit Mux Registers Main Control ALU Control ALU AND Shift Left2 Sign Extend Branch Adder Data Memory 60 ps 15ps 120 ps 50 ps, 25 ps, 150 ps 5 ps 10 ps(Shiftleft2jump also) 15 ps 60 ps 150 ps C) Do a stagewise latency analysis of the circuit. Write down signal timings on the stagevise, single cycle CPU diagram provided. Reset the time to zero every time any signal crosses a stage boundary. Calculate the latency and highlight the critical path for each stage i What will be the clock rate of a pipelined CPU based on this circuit? (ii Ifyou were asked to increase the clock rate of the pipelined CPU by designing a faster ALU by how much will you be able to reduce its latency beyond which it would make no difference

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts