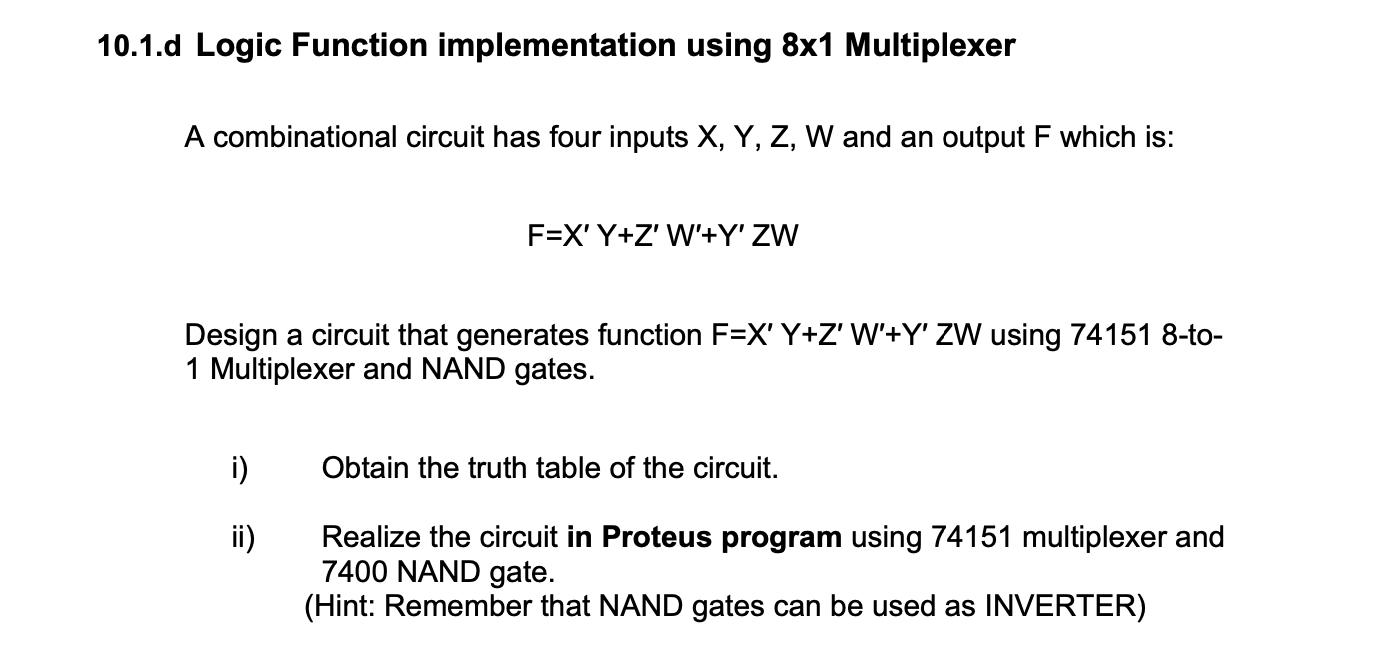

Question: 0.1.d Logic Function implementation using 8x1 Multiplexer A combinational circuit has four inputs X,Y,Z,W and an output F which is: F=XY+ZW+YZW Design a circuit that

0.1.d Logic Function implementation using 8x1 Multiplexer A combinational circuit has four inputs X,Y,Z,W and an output F which is: F=XY+ZW+YZW Design a circuit that generates function F=XY+ZW+YZW using 74151 8-to1 Multiplexer and NAND gates. i) Obtain the truth table of the circuit. ii) Realize the circuit in Proteus program using 74151 multiplexer and 7400 NAND gate. (Hint: Remember that NAND gates can be used as INVERTER)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts