Question: 1. (10 points) Assume a 64 entry write-through, direct mapped cache with 4 words per block. The system uses 32-bit addresses and a data

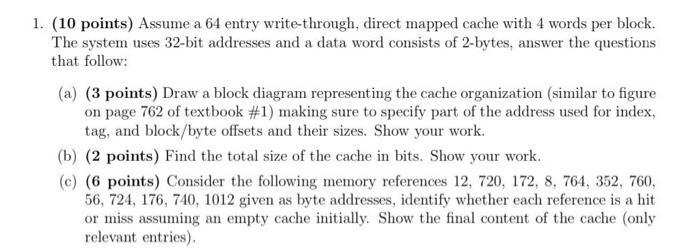

1. (10 points) Assume a 64 entry write-through, direct mapped cache with 4 words per block. The system uses 32-bit addresses and a data word consists of 2-bytes, answer the questions that follow: (a) (3 points) Draw a block diagram representing the cache organization (similar to figure on page 762 of textbook #1) making sure to specify part of the address used for index, tag, and block/byte offsets and their sizes. Show your work. (b) (2 points) Find the total size of the cache in bits. Show your work. (c) (6 points) Consider the following memory references 12, 720, 172, 8, 764, 352, 760, 56, 724, 176, 740, 1012 given as byte addresses, identify whether each reference is a hit or miss assuming an empty cache initially. Show the final content of the cache (only relevant entries).

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts