Question: 1. Complete the pipeline execution diagram for the code below, if a 5-stage processor has forwarding from MEM stage to EX stage and WB stage

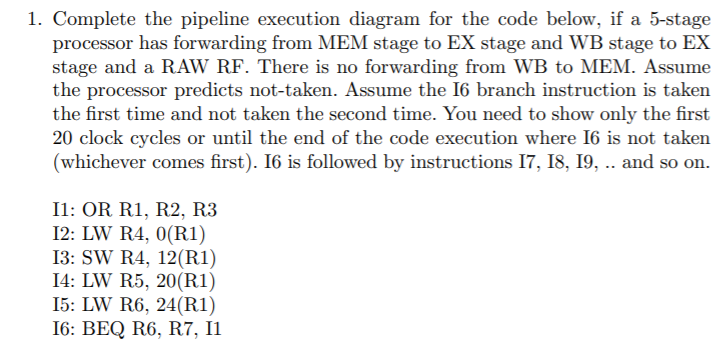

1. Complete the pipeline execution diagram for the code below, if a 5-stage processor has forwarding from MEM stage to EX stage and WB stage to EX stage and a RAW RF. There is no forwarding from WB to MEM. Assume the processor predicts not-taken. Assume the 16 branch instruction is taken the first time and not taken the second time. You need to show only the first 20 clock cycles or until the end of the code execution where 16 is not taken (whichever comes first). 16 is followed by instructions 17, 18, 19, .. and so on. I1: OR R1, R2, R3 12: LW R4, 0(R1) 13: SW R4, 12(R1) 14: LW R5, 20(R1) 15: LW R6, 24(R1) 16: BEQ R6, R7, 11 1. Complete the pipeline execution diagram for the code below, if a 5-stage processor has forwarding from MEM stage to EX stage and WB stage to EX stage and a RAW RF. There is no forwarding from WB to MEM. Assume the processor predicts not-taken. Assume the 16 branch instruction is taken the first time and not taken the second time. You need to show only the first 20 clock cycles or until the end of the code execution where 16 is not taken (whichever comes first). 16 is followed by instructions 17, 18, 19, .. and so on. I1: OR R1, R2, R3 12: LW R4, 0(R1) 13: SW R4, 12(R1) 14: LW R5, 20(R1) 15: LW R6, 24(R1) 16: BEQ R6, R7, 11

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts