Question: 1. Consider a CPU with a simple non-pipelined data path. The registers A, B, MDR and the ALU are all 8-bit wide. SP and

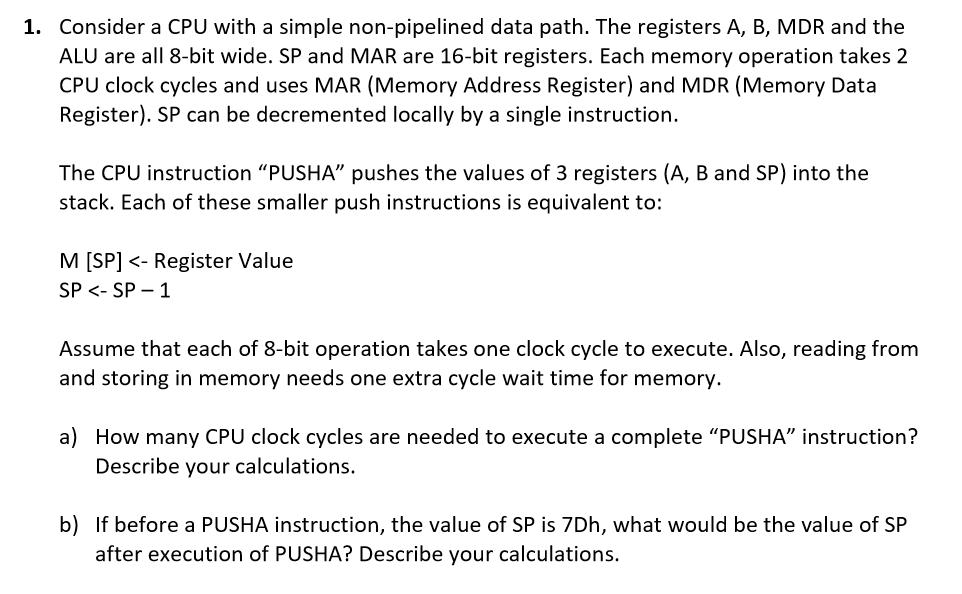

1. Consider a CPU with a simple non-pipelined data path. The registers A, B, MDR and the ALU are all 8-bit wide. SP and MAR are 16-bit registers. Each memory operation takes 2 CPU clock cycles and uses MAR (Memory Address Register) and MDR (Memory Data Register). SP can be decremented locally by a single instruction. The CPU instruction "PUSHA" pushes the values of 3 registers (A, B and SP) into the stack. Each of these smaller push instructions is equivalent to: M [SP] < Register Value SP - SP-1 Assume that each of 8-bit operation takes one clock cycle to execute. Also, reading from and storing in memory needs one extra cycle wait time for memory. a) How many CPU clock cycles are needed to execute a complete "PUSHA" instruction? Describe your calculations. b) If before a PUSHA instruction, the value of SP is 7Dh, what would be the value of SP after execution of PUSHA? Describe your calculations.

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts