Question: 1 . Consider a simple MIPS - like pipeline with the following stages: IF: Instruction Fetch ID: Instruction Decode EX: Execute MEM: Memory Access WB:

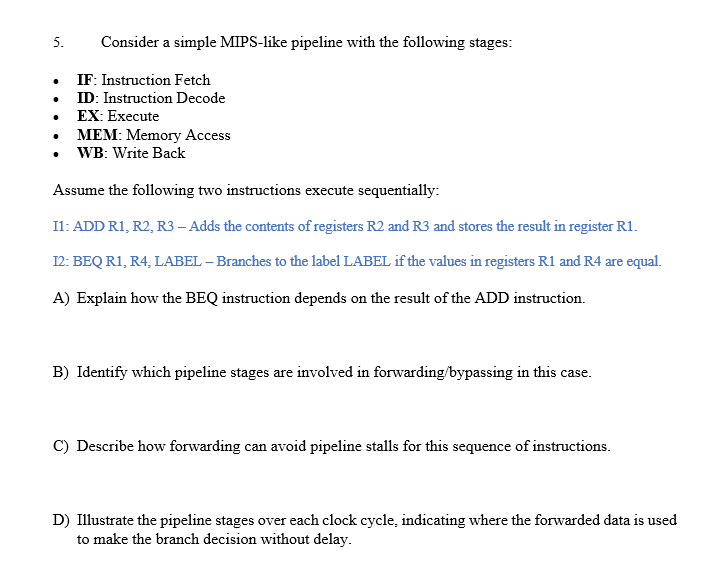

Consider a simple MIPSlike pipeline with the following stages:

IF: Instruction Fetch

ID: Instruction Decode

EX: Execute

MEM: Memory Access

WB: Write Back

Assume the following two instructions execute sequentially:

I: ADD R R R Adds the contents of registers R and R and stores the result in register R

I: BEQ R R LABEL Branches to the label LABEL if the values in registers R and R are equal.

A Explain how the BEQ instruction depends on the result of the ADD instruction.

B Identify which pipeline stages are involved in forwardingbypassing in this case.

C Describe how forwarding can avoid pipeline stalls for this sequence of instructions.

D Illustrate the pipeline stages over each clock cycle, indicating where the forwarded data is used to make the branch decision without delay. Consider a simple MIPSlike pipeline with the following stages:

IF: Instruction Fetch

ID: Instruction Decode

EX: Execute

MEM: Memory Access

WB: Write Back

Assume the following two instructions execute sequentially:

I: ADD R R R Adds the contents of registers R and R and stores the result in register R

I: BEQ R R LABEL Branches to the label LABEL if the values in registers R and R are equal.

A Explain how the BEQ instruction depends on the result of the ADD instruction.

B Identify which pipeline stages are involved in forwardingbypassing in this case.

C Describe how forwarding can avoid pipeline stalls for this sequence of instructions.

D Illustrate the pipeline stages over each clock cycle, indicating where the forwarded data is used to make the branch decision without delay.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock