Question: 1. Consider the following assembly code. 1. LOAD R, #1 2. LOAD SA #1 3. LOAD T, #(k-3) 4. ADD AC, R, S 5. LOADR,

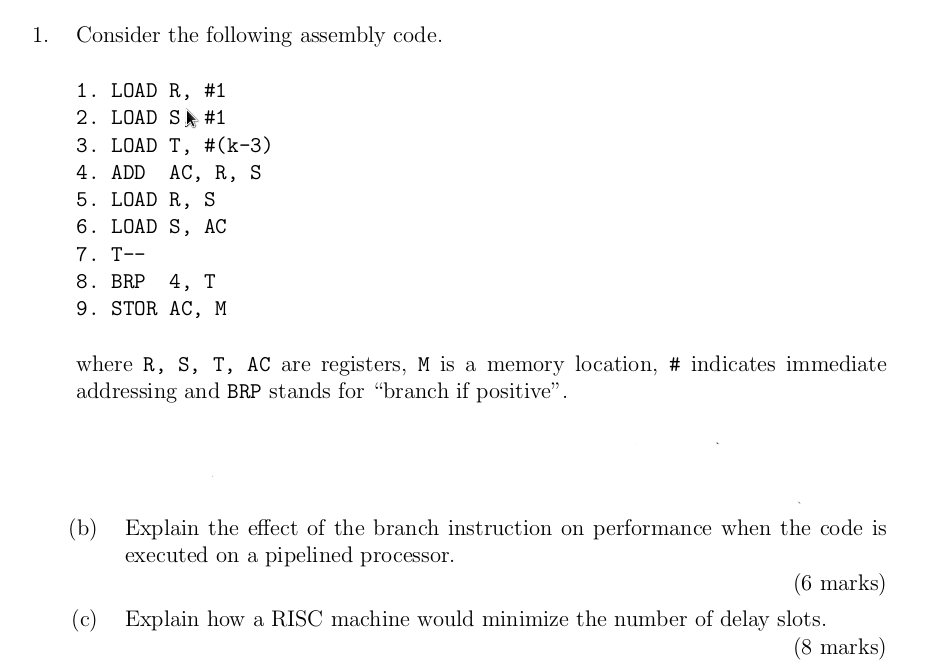

1. Consider the following assembly code. 1. LOAD R, #1 2. LOAD SA #1 3. LOAD T, #(k-3) 4. ADD AC, R, S 5. LOADR, S 6. LOAD S, AC 7. T 8. BRP 4, T 9. STOR AC, M where R, S, T, AC are registers. M is a memory location. # indicates immediate addressing and BRP stands for "branch if positive" (b) Explain the effect of the branch instruction on performance when the code is executed on a pipelined processor. (6 marks) (c) Explain how a RISC machine would minimize the number of delay slots (8 marks)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts