Question: 1. Given the following MIPS instructions, if we only implement the following hazard detection unit without the forwarding control capacity, (1) please identify what problems

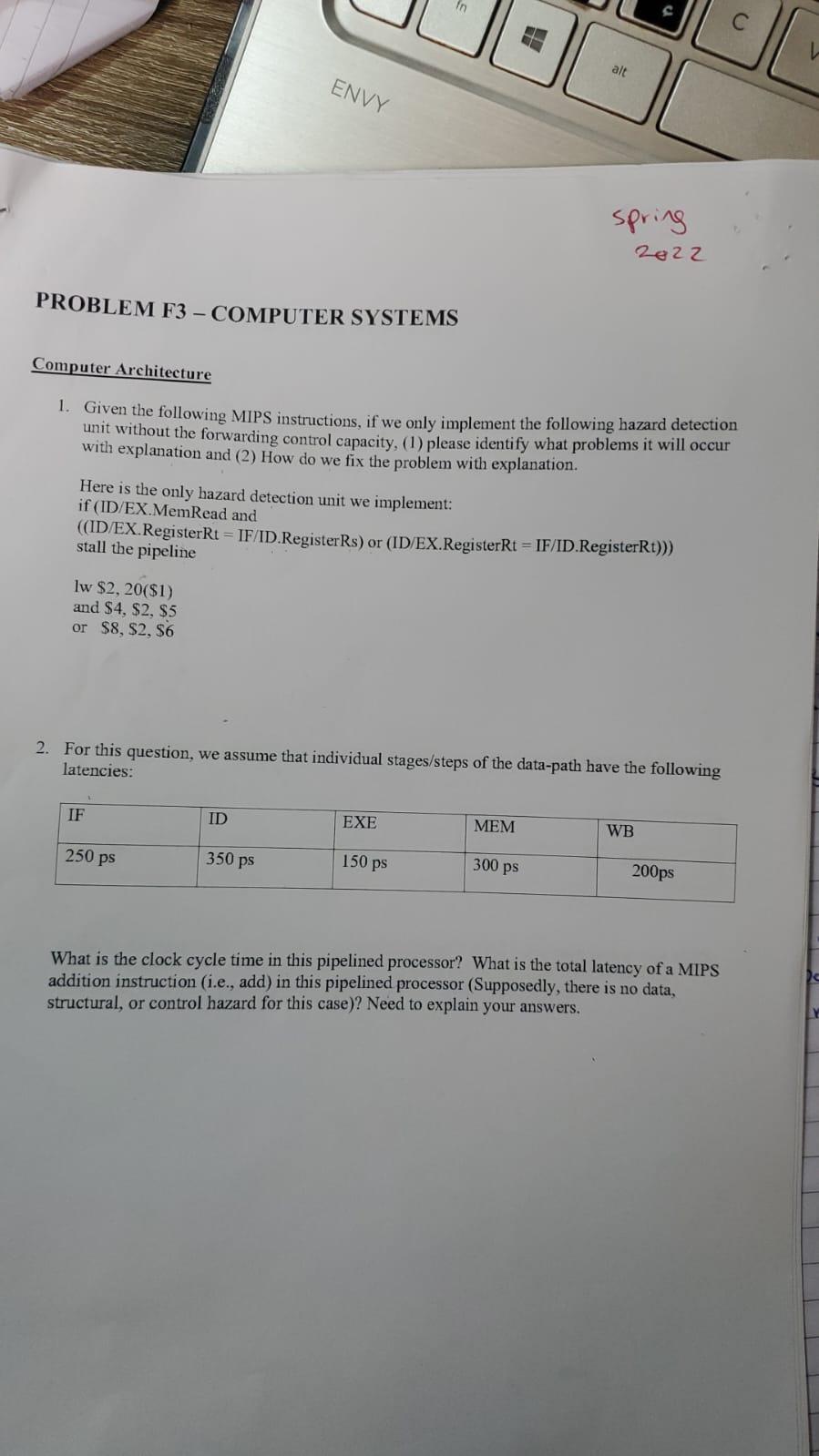

1. Given the following MIPS instructions, if we only implement the following hazard detection unit without the forwarding control capacity, (1) please identify what problems it will occur with explanation and (2) How do we fix the problem with explanation. Here is the only hazard detection unit we implement: if (ID/EX.MemRead and ((ID/EX.RegisterRt = IF/ID.RegisterRs ) or ( ID/EX.RegisterRt = IF/ID.RegisterRt )) ) stall the pipeline lw $2,20($1) and $4,$2,$5 or $8,$2,$6 2. For this question, we assume that individual stages/steps of the data-path have the following latencies: What is the clock cycle time in this pipelined processor? What is the total latency of a MIPS addition instruction (i.e., add) in this pipelined processor (Supposedly, there is no data, structural, or control hazard for this case)? Need to explain your answers

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts