Question: 1. You will design a multiplication circuit which has 2 inputs : 5 bit multiplicand (binary) and 5 bit multiplier(binary). The circuit should apply the

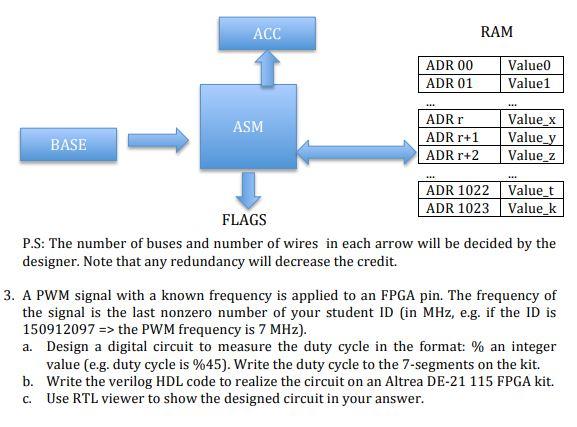

1. You will design a multiplication circuit which has 2 inputs : 5 bit multiplicand (binary) and 5 bit multiplier(binary). The circuit should apply the following multiplication rules: Multiply the multiplicand by two 'k' times, here 'k' is the maximum value that still allows to determine the result by using sum opertion. Then add multiplicand 'r' times to the multiplicand*2\) to determine the result. Here Y' is (multiplier - 24). See the examples below. E.g.1: 24x12 = 24*2*2*2 + (24 +24+24 +24) = 288 E.g.2: 31x22 = 31*2*2*2*2 + (31+31+31+31+31+31) = 682 a. Design the circuit and explain the design principles detailed enough. The design must include a moore type finite state machine and the required peripherals. b. Plot your circuit using the blocks, give the structure of each block using and/orot Gates. 2. Design an Algorithmic state machine (ASM) that adds 'n' consequtive values inside RAM space from address

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts