Question: [10] Consider following loop: Loop LW r2, e(r2) r2, re, LOOP r2, r2, r3 r2, e(r5) BEQ SW Assume that there is no delay slot

![[10] Consider following loop: Loop LW r2, e(r2) r2, re, LOOP](https://s3.amazonaws.com/si.experts.images/answers/2024/08/66cda554af5c3_23666cda55460634.jpg)

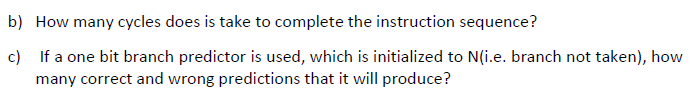

[10] Consider following loop: Loop LW r2, e(r2) r2, re, LOOP r2, r2, r3 r2, e(r5) BEQ SW Assume that there is no delay slot and the nextPC in located in ID stage. Also assume that the loop is iterated for 100 times. a) Draw the pipeline diagram for the first 2 iterations [10] Consider following loop: Loop LW r2, e(r2) r2, re, LOOP r2, r2, r3 r2, e(r5) BEQ SW Assume that there is no delay slot and the nextPC in located in ID stage. Also assume that the loop is iterated for 100 times. a) Draw the pipeline diagram for the first 2 iterations

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts