Question: 10. The RTN for the first step in the fetch-decode-execute cycle is: A) MAR PC B) PC PC1 D) IR-MBR 11. During the first pass

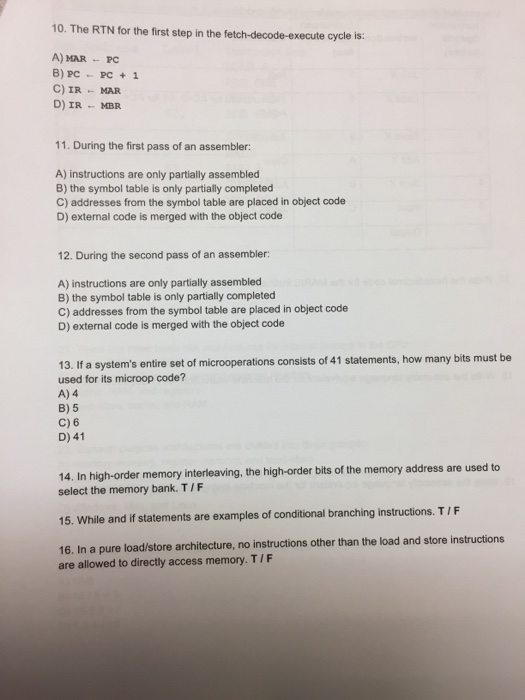

10. The RTN for the first step in the fetch-decode-execute cycle is: A) MAR PC B) PC PC1 D) IR-MBR 11. During the first pass of an assembler A) instructions are only partially assembled B) the symbol table is only partially completed C) addresses from the symbol table are placed in object code D) external code is merged with the object code 12. During the second pass of an assembler: A) instructions are only partially assembled B) the symbol table is only partially completed C) addresses from the symbol table are placed in object code D) external code is merged with the object code 13. If a system's entire set of microoperations consists of 41 statements, how many bits must be used for its microop code? A) 4 B) 5 C) 6 D)41 14. In h igh-order memory interleaving, the high-order bits of the memory address are used to select the memory bank. T/F 15. While and if statements are examples of conditional branching instructions. T/F 16. In a pure load/store architecture, no instructions other than the load and store instructions are allowed to directly access memory. T/F

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts