Question: [12] Data Path Cycles: Use the following data to answer the questions below: Instruction Memory: 150 ps. Data Memory ALU and adders:100 ps Register File:

![[12] Data Path Cycles: Use the following data to answer the](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f325ad15c1b_92466f325ac99099.jpg)

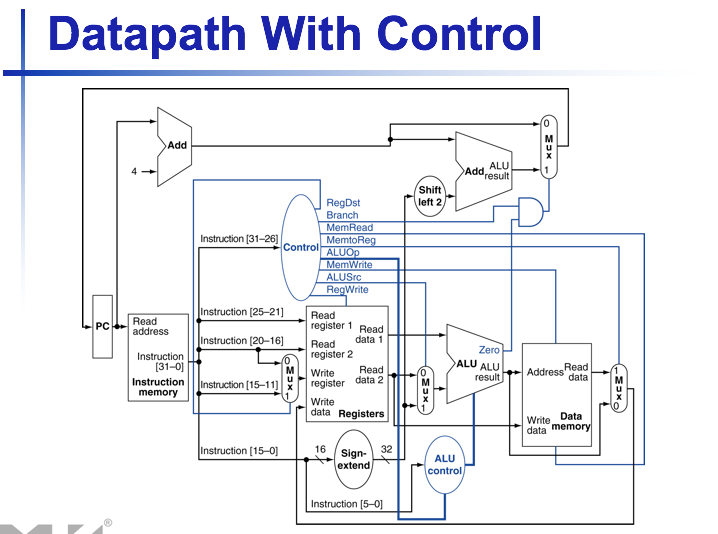

[12] Data Path Cycles: Use the following data to answer the questions below: Instruction Memory: 150 ps. Data Memory ALU and adders:100 ps Register File: Assume that mux, control unit, PC accesses, sign extension unit and wires have no latency 250 ps 50 ps Load_ 1. Using the datapath diagram given for Part 2, determine the time that eachStore of the types of instructions would require. BEQ JUMP 2. If every instruction executes in 1 clock cycle of a fixed length, what is the 2. length of one clock cycle? 3. If every instruction executes in 1 clock cycle using a variable length clock, with an instruction mix of 15% loads, 25% stores, 45% ALU type, 11% branches and 4% jumps, what is the average length clock cycle? | 3. Load_ Store BEQ JUMP- 4. If the datapath is evaluated by letting each stage of execution determine the cycle time, which allows us to use a pipelined design, how many stages are used by each type of instruction? 5. In order to use a pipelined design for the datapath, what would be the length of a cycle (in ps)? 6. Using a pipelined design and the above mix of instructions, where a jump always causes a 1 cycle delay, 30% of the load instructions are immediately followed by an instruction that uses the result (causing a 1-cyle6. delay), and 15% of the branch instructions are mis-directed (causing a 2- cycle delay). What is the average effective number of cycles once the pipeline is loaded

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts