Question: Data Path Cycles Use the following data to answer the questions below: Instruction Memorny Data Memory ALU and adders Register File Assume that mux, control

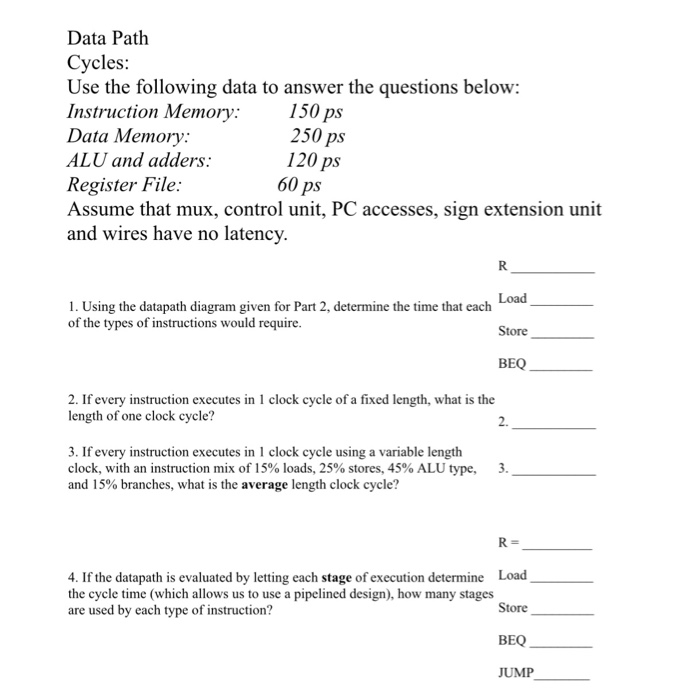

Data Path Cycles Use the following data to answer the questions below: Instruction Memorny Data Memory ALU and adders Register File Assume that mux, control unit, PC accesses, sign extension unit and wires have no latency. 150 ps 250 ps 120 ps 60 ps Load_ Store BEQ 1. Using the datapath diagram given for Part 2, determine the time that each of the types of instructions would require. 2. If every instruction executes in 1 clock cycle of a fixed length, what is the length of one clock cycle? 2. 3. If every instruction executes in 1 clock cycle using a variable length clock, with an instruction mix of 15% loads, 25% stores, 45% ALU type, and 15% branches, what is the average length clock cycle? 3. 4. If the datapath is evaluated by letting each stage of execution determine Load the cycle time (which allows us to use a pipelined design), how many stages are used by each type of instruction? Store BEQ JUMP

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts