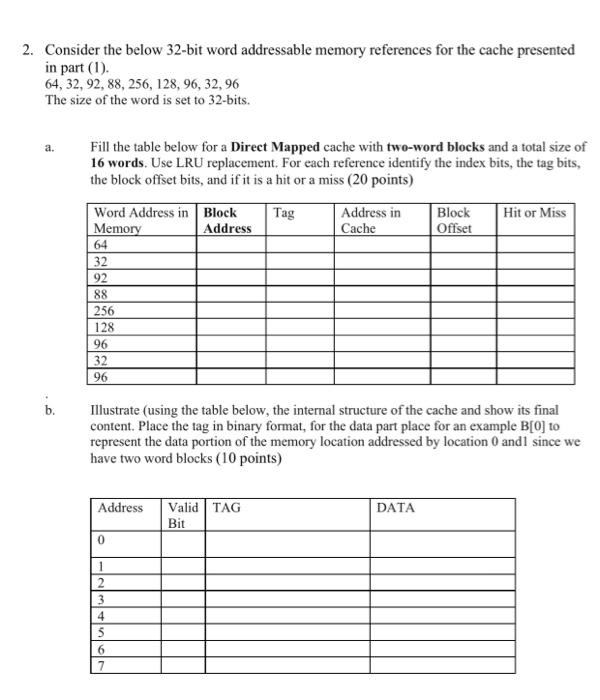

Question: 2. Consider the below 32-bit word addressable memory references for the cache presented in part (1). 64, 32, 92, 88, 256, 128,96, 32,96 The size

2. Consider the below 32-bit word addressable memory references for the cache presented in part (1). 64, 32, 92, 88, 256, 128,96, 32,96 The size of the word is set to 32-bits. Fill the table below for a Direct Mapped cache with two-word blocks and a total size of 16 words. Use LRU replacement. For each reference identify the index bits, the tag bits, the block offset bits, and if it is a hit or a miss (20 points) Word Address in Block Tag Address in Block Hit or Miss Memory Address Cache Offset 64 32 92 88 256 128 96 32 96 b. Illustrate (using the table below, the internal structure of the cache and show its final content. Place the tag in binary format, for the data part place for an example B[0] to represent the data portion of the memory location addressed by location 0 and since we have two word blocks (10 points) Address Valid | TAG Bit DATA 0 1 2 3 4 5 6 7

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts