Question: 2- Now imagine that we take the pseudo-CPU (from problem 1) and add a Stack Pointer (SP). Suppose the pseudo- CPU can be used to

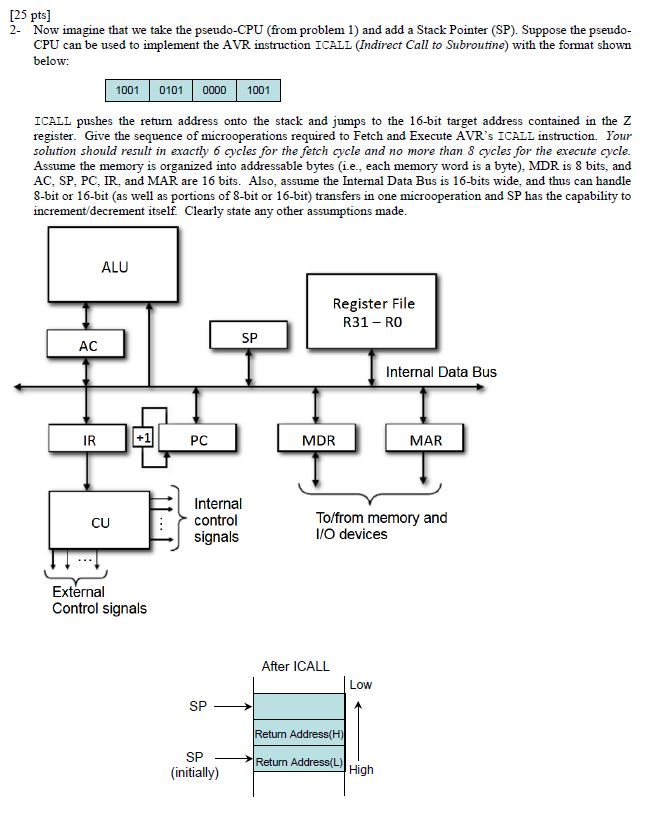

2- Now imagine that we take the pseudo-CPU (from problem 1) and add a Stack Pointer (SP). Suppose the pseudo- CPU can be used to implement the AVR instruction ICALL (Indirect Call to Subroutine) with the format shown below: ICALL pushes the return address onto the stack and jumps to the 16-bit target address contained in the Z register. Give the sequence of microoperations required to Fetch and Execute AVRs ICALL instruction. Your solution should result in exactly 6 cycles for the fetch cycle and no more than 8 cycles for the execute cycle. Assume the memory is organized into addressable bytes (i.e., each memory word is a byte), MDR is 8 bits, and AC, SP, PC, IR, and MAR are 16 bits. Also, assume the Internal Data Bus is 16-bits wide, and thus can handle 8-bit or 16-bit (as well as portions of 8-bit or 16-bit) transfers in one microoperation and SP has the capability to increment/decrement itself. Clearly state any other assumptions made.

[25 pts] 2- Now imagine that we take the pseudo-CPU (from problem 1) and add a Stack Pointer (SP). Suppose the pseudo- CPU can be used to implement the AVR instruction ICALL (Indirect Call to Subroutine) with the format shown below: 1001 0101 0000 1001 ICALL pushes the retum address onto the stack and jumps to the 16-bit target address contained in the Z register. Give the sequence of microoperations required to Fetch and Execute AVR'S ICALL instruction. Your solution should result in exactly 6 cycles for the fetch cycle and no more than 8 cycles for the execute cycle. Assume the memory is organized into addressable bytes (i.e., each memory word is a byte), MDR is 8 bits, and AC, SP, PC, IR, and MAR are 16 bits. Also, assume the Internal Data Bus is 16-bits wide, and thus can handle 8-bit or 16-bit (as well as portions of 8-bit or 16-bit) transfers in one microoperation and SP has the capability to increment/decrement itself. Clearly state any other assumptions made. ALU Register File R31 - RO SP Internal Data Bus Internal control signals To/from memory and I/O devices External Control signals After ICALL Low SP Retur Address(H) SP Return Addressil High (initially) [25 pts] 2- Now imagine that we take the pseudo-CPU (from problem 1) and add a Stack Pointer (SP). Suppose the pseudo- CPU can be used to implement the AVR instruction ICALL (Indirect Call to Subroutine) with the format shown below: 1001 0101 0000 1001 ICALL pushes the retum address onto the stack and jumps to the 16-bit target address contained in the Z register. Give the sequence of microoperations required to Fetch and Execute AVR'S ICALL instruction. Your solution should result in exactly 6 cycles for the fetch cycle and no more than 8 cycles for the execute cycle. Assume the memory is organized into addressable bytes (i.e., each memory word is a byte), MDR is 8 bits, and AC, SP, PC, IR, and MAR are 16 bits. Also, assume the Internal Data Bus is 16-bits wide, and thus can handle 8-bit or 16-bit (as well as portions of 8-bit or 16-bit) transfers in one microoperation and SP has the capability to increment/decrement itself. Clearly state any other assumptions made. ALU Register File R31 - RO SP Internal Data Bus Internal control signals To/from memory and I/O devices External Control signals After ICALL Low SP Retur Address(H) SP Return Addressil High (initially)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts