Question: 3. a. For set-Associative mapping if Main Memory: 64GB, Block/Line Size: 16B, Cache:512 KB with 4- way set associative: [4] i. How many address

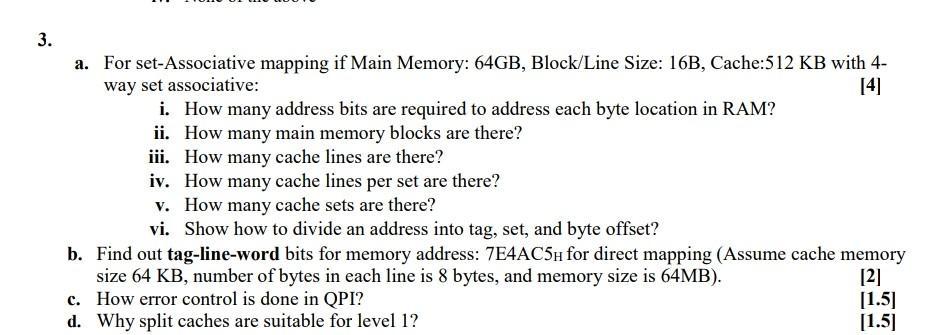

3. a. For set-Associative mapping if Main Memory: 64GB, Block/Line Size: 16B, Cache:512 KB with 4- way set associative: [4] i. How many address bits are required to address each byte location in RAM? ii. How many main memory blocks are there? iii. How many cache lines are there? iv. How many cache lines per set are there? v. How many cache sets are there? vi. Show how to divide an address into tag, set, and byte offset? b. Find out tag-line-word bits for memory address: 7E4AC5H for direct mapping (Assume cache memory size 64 KB, number of bytes in each line is 8 bytes, and memory size is 64MB). [2] c. How error control is done in QPI? d. Why split caches are suitable for level 1? [1.5] [1.5]

Step by Step Solution

3.45 Rating (155 Votes )

There are 3 Steps involved in it

3a SetAssociative Mapping Given parameters Main Memory 64GB 64 1024 MB BlockLine Size 16B Cache 512 KB 512 1024 Bytes with 4way set associative i Addr... View full answer

Get step-by-step solutions from verified subject matter experts