Question: Ex 5 : Cache Performance Analysis A CPU produces the following sequence of read addresses in hexadecimal: 1 A , 2 C , 3 E

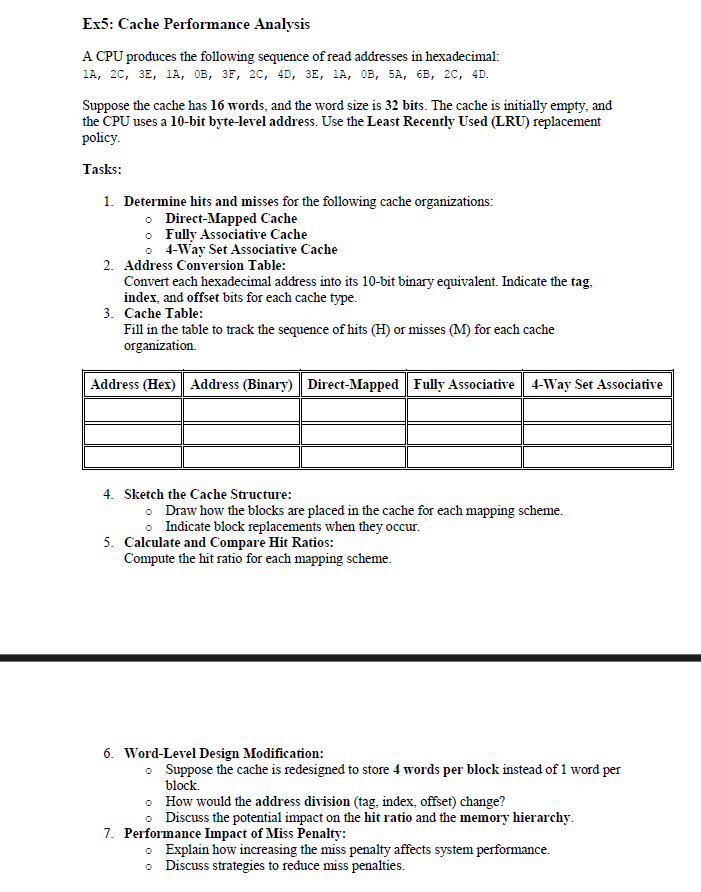

Ex: Cache Performance Analysis

A CPU produces the following sequence of read addresses in hexadecimal:

ACEABFCDEABABCD

Suppose the cache has words, and the word size is bits. The cache is initially empty, and

the CPU uses a bit bytelevel address. Use the Least Recently Used LRU replacement

policy.

Tasks:

Determine hits and misses for the following cache organizations:

DirectMapped Cache

Fully Associative Cache

Way Set Associative Cache

Address Conversion Table:

Convert each hexadecimal address into its bit binary equivalent. Indicate the tag,

index, and offset bits for each cache type.

Cache Table:

Fill in the table to track the sequence of hits H or misses M for each cache

organization.

Sketch the Cache Structure:

Draw how the blocks are placed in the cache for each mapping scheme.

Indicate block replacements when they occur.

Calculate and Compare Hit Ratios:

Compute the hit ratio for each mapping scheme.

WordLevel Design Modification:

Suppose the cache is redesigned to store words per block instead of word per

block.

How would the address division tag index, offset change?

Discuss the potential impact on the hit ratio and the memory hierarchy.

Performance Impact of Miss Penalty:

Explain how increasing the miss penalty affects system performance.

Discuss strategies to reduce miss penalties.

Ex:

Memory Chip Design

How many K chips are needed to provide a RAM of M

Tasks:

o Determine the number of chips required.

o Design the RAM chip layout.

o Specify all the inputs and outputs required for the design.

GPU Acceleration and Amdahls Law

A computation runs times faster on the GPU compared to the CPU. Assume that of the program can be accelerated using the GPU.

Tasks:

o Calculate the overall speedup using Amdahls Law.

o If the program requires an overall speedup of determine the percentage of the program that must be accelerated using the GPU.

Virtual Memory and Page Tables

In a multitasking system with virtual memory:

Page size: kB

Page table entry size: bits

The number of pages per program:

o Program X: pages

o Program Y: pages

o Program Z: pages

Tasks:

Calculate the total memory occupied by the page tables for all three programs in bytes.

If each program requires a directory for regions, where each directory entry is bytes, calculate the total memory occupied by the directory pages.

SpeedUp with Multiple Processors

Two computations are performed:

A scalar sum of variables.

A matrix sum of twodimensional arrays of dimensions

Tasks:

Calculate the speedup using processors versus processors, assuming perfect parallelism.

Discuss the effect of diminishing returns as the number of processors increases.

Cache Design and Address Decomposition

a Show the address decomposition for a kB directmapped cache with a byte block size using a bit address.

Identify the tag, index, and offset bits.

b For a directmapped cache with the following address division:

TAG: Bits

INDEX: Bits

BYTE OFFSET: Bits

Tasks:

Determine the cache line size in bytes.

Calculate the number of cache entries.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock