Question: 3- An 8 bit CPU having 64kBytes addressing capability will be connected to a memory block that contains 1 piece of 27C256 EPROM, 1 piece

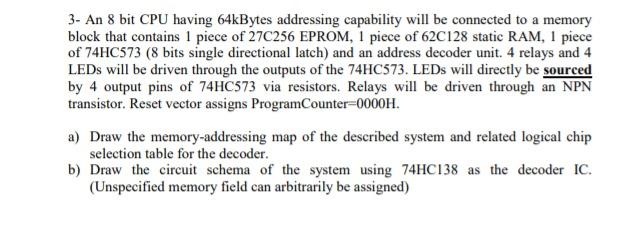

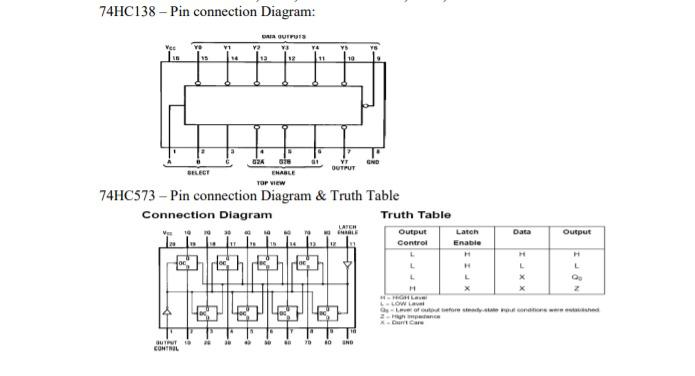

3- An 8 bit CPU having 64kBytes addressing capability will be connected to a memory block that contains 1 piece of 27C256 EPROM, 1 piece of 62C128 static RAM, 1 piece of 74HC573 (8 bits single directional latch) and an address decoder unit. 4 relays and 4 LEDs will be driven through the outputs of the 74HC573. LEDs will directly be sourced by 4 output pins of 74HC573 via resistors. Relays will be driven through an NPN transistor. Reset vector assigns ProgramCounter-0000H. a) Draw the memory-addressing map of the described system and related logical chip selection table for the decoder. b) Draw the circuit schema of the system using 74HC138 as the decoder IC. (Unspecified memory field can arbitrarily be assigned) 74HC138 - Pin connection Diagram: A GUIPUIS Y1 Y Y4 YS AB 15 Y 10 12 11 G2A GND SELECT ENABLE OUTPUT TOP VIEW 74HC573 - Pin connection Diagram & Truth Table Connection Diagram Truth Table 30 LATEH ENRALE Data Output Control Laten Enable Output H re ST X HOLY - LOW we offered the care 10 10 IND CONTROL

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts