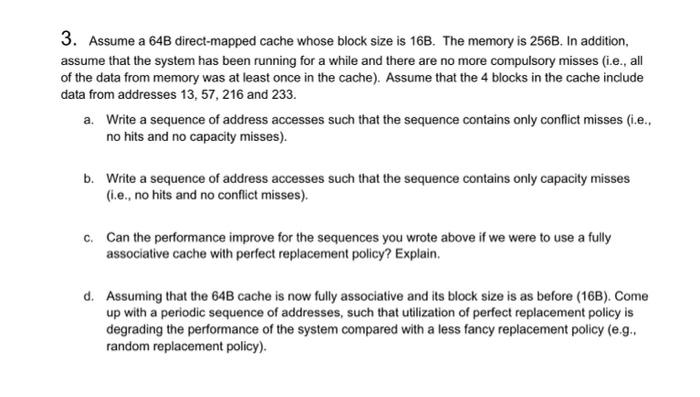

Question: 3. Assume a 64B direct-mapped cache whose block size is 16B. The memory is 256B. In addition, assume that the system has been running for

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock