Question: 4. For a multi-cycle processor, assume that the operation times for the major function units are as following 1) Memory units: 200 ps; 2) ALU

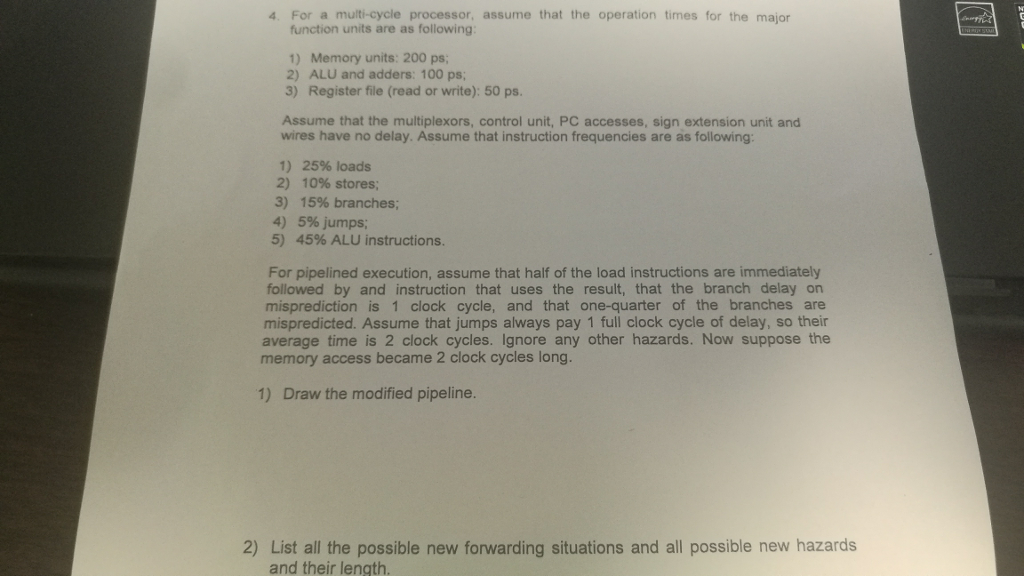

4. For a multi-cycle processor, assume that the operation times for the major function units are as following 1) Memory units: 200 ps; 2) ALU and adders: 100 ps 3) Register file (read or write): 50 ps Assume that the multiplexors, control unit, PC accesses, sign extension unit and wires have no delay. Assume that instruction frequencies are as following 1) 25% loads 2) 10% stores; 3) 15% branches; 4) 5% jumps, 5) 45%ALU instructions. For pipelined execution, assume that half of the load instructions are immediately followed by and instruction that uses the result, that the branch delay on misprediction is 1 clock cycle, and that one-quarter of the branches are mispredicted. Assume that jumps always pay 1 full clock cycle of delay, so their average time is 2 clock cycles. Ignore any other hazards. Now suppose the memory access became 2 clock cycles long. 1) Draw the modified pipeline. 2) List all the possible new forwarding situations and all possible new hazards and their length

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts