Question: 4. In class, we studied the single cycle datapath for the MIPS processor which has a 32-element 32-bit register file with two read ports

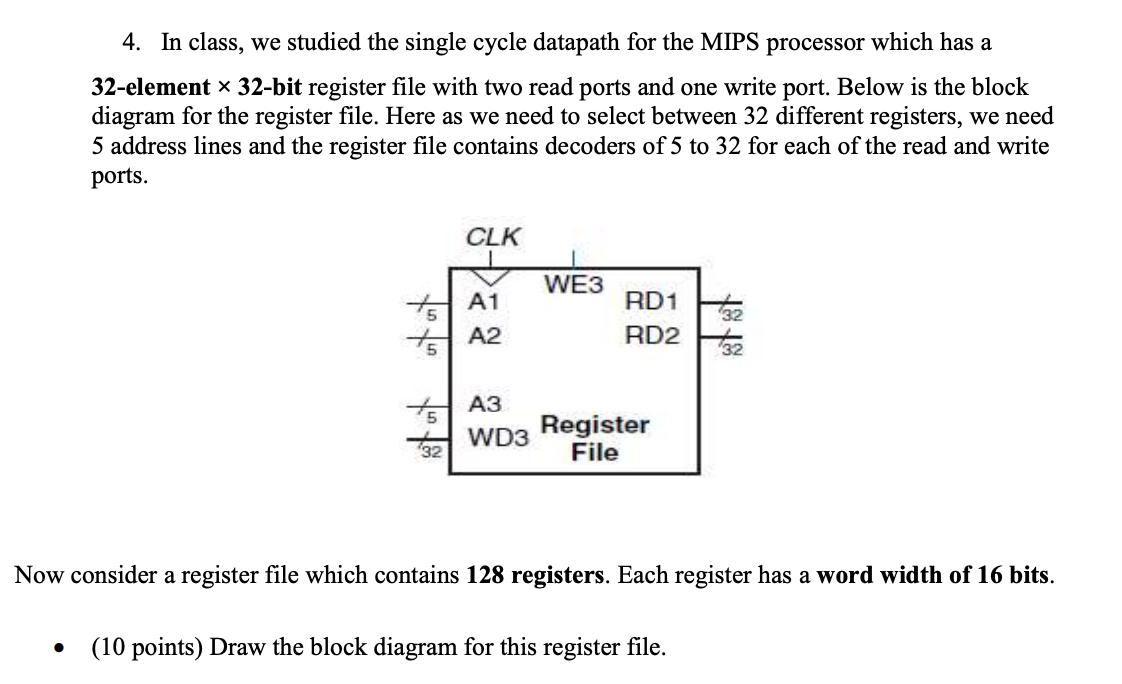

4. In class, we studied the single cycle datapath for the MIPS processor which has a 32-element 32-bit register file with two read ports and one write port. Below is the block diagram for the register file. Here as we need to select between 32 different registers, we need 5 address lines and the register file contains decoders of 5 to 32 for each of the read and write ports. CLK WE3 A1 RD1 A2 RD2 A3 WD3 Register File Now consider a register file which contains 128 registers. Each register has a word width of 16 bits. (10 points) Draw the block diagram for this register file. (5 points) How many one bit register cells are needed to implement this register file? (5 points) What type of decoder is required for the A1, A2, and A3? (i.e., an n to m decoder).

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts